层叠结构不变的情况下,增加线宽,损耗,串扰变化

虽然简单,但是比较有意思,大家可以来思考一下

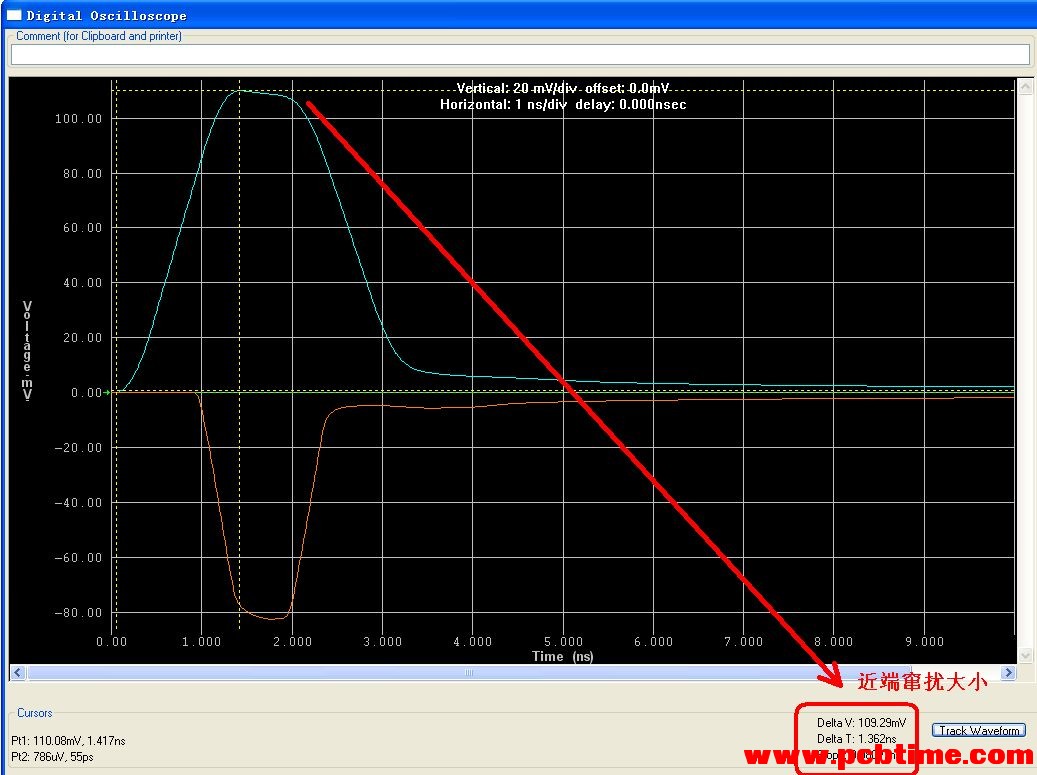

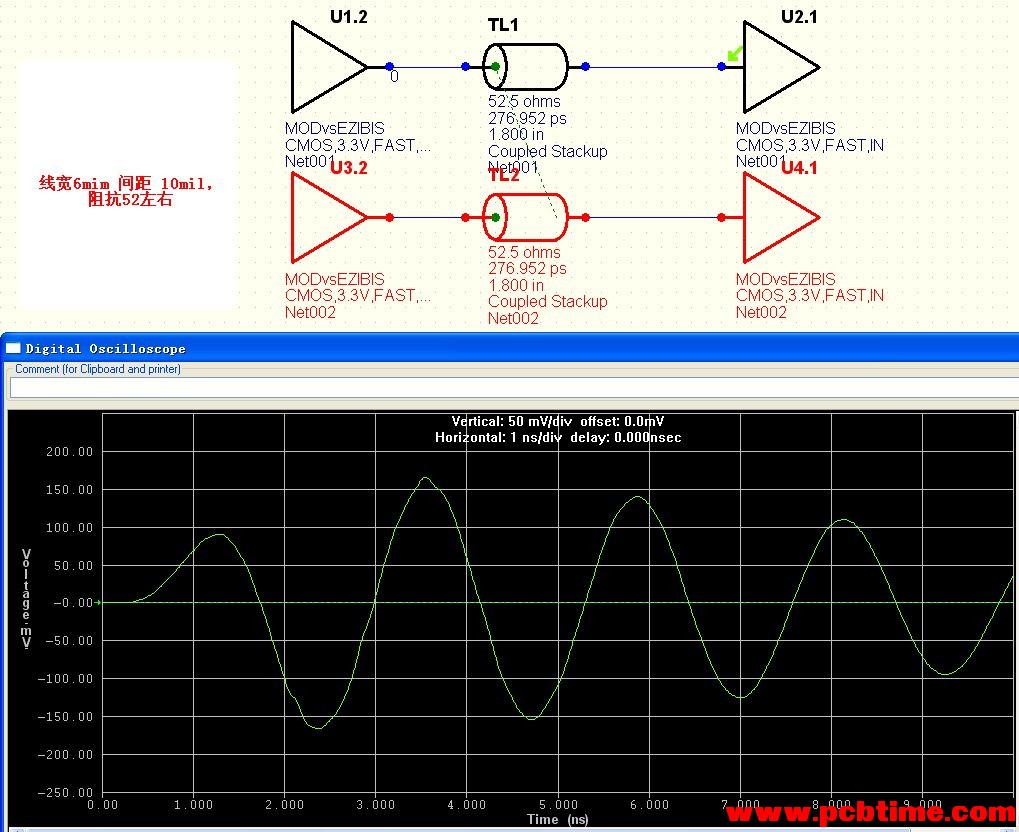

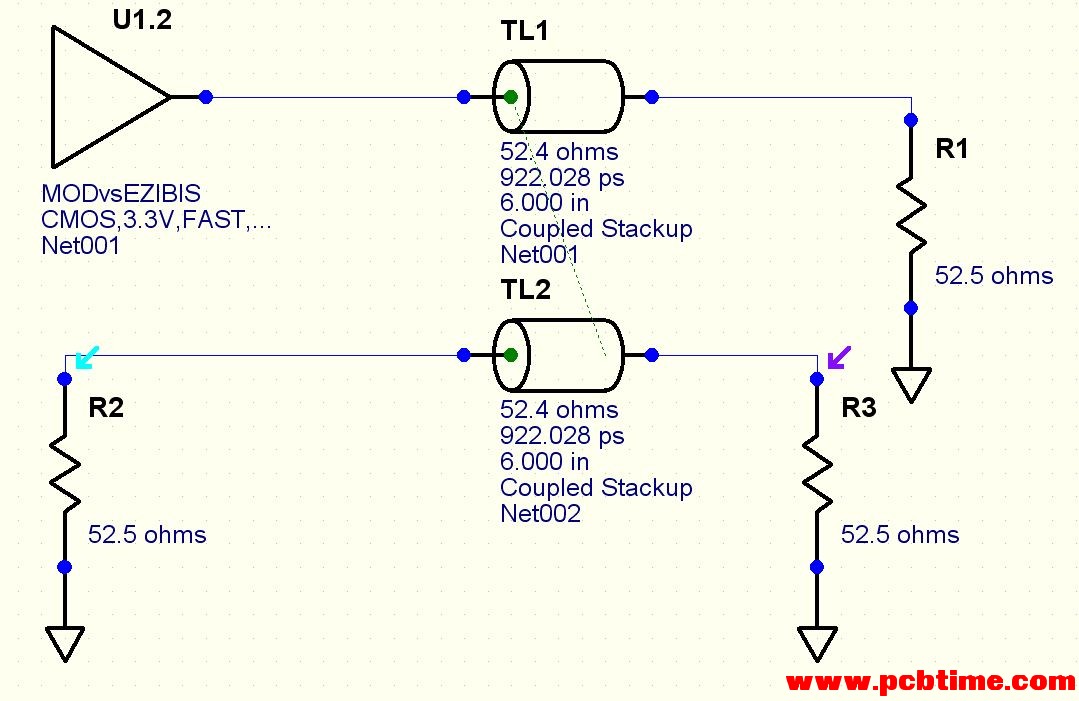

在hyperlynx仿真的话直接在攻击线上加一个驱动,末端用电阻跟传输线匹配。

静态线两端都端接匹配电阻到地,测量静态线上两端电阻上的电压就可以比较他们的近端与远端串扰了。

比如原来的层叠,走线是6mil线宽,和其他线是10mil距离

线宽加到8mil,间距相应减小为8mil

层叠不表,其他条件都不变

最简单的是阻抗,线宽增加,阻抗减小

串扰呢,线间距减小,串扰会显著增大吗?

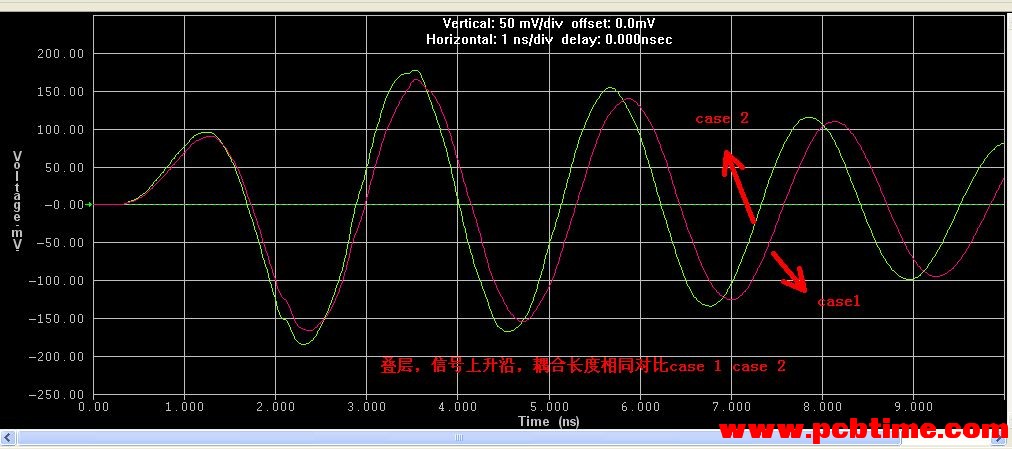

case1 VS case2

这个仿真考虑了信号的反射没有?考虑的东西太少很容易仿出个错误的结果得到个错误的结论哦··

哦,楼上的老师请教一下,如果在考虑到反射的因素后由于阻抗不匹配引起的这部分窜扰,怎样控制case1,和case2的反射引起的窜扰是一致的,感谢

OK ,感谢了,3Q

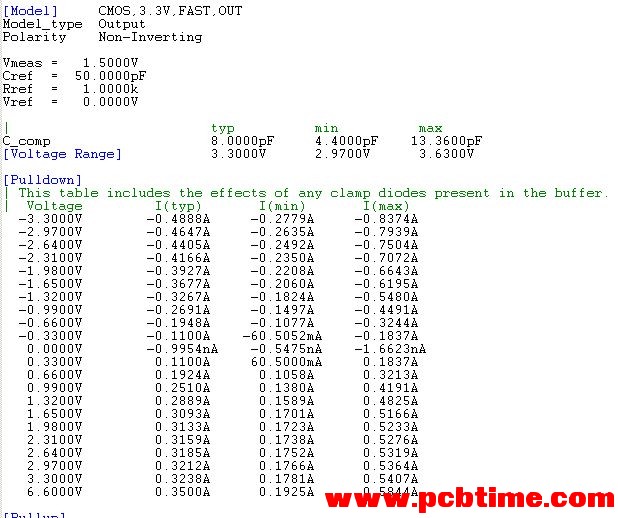

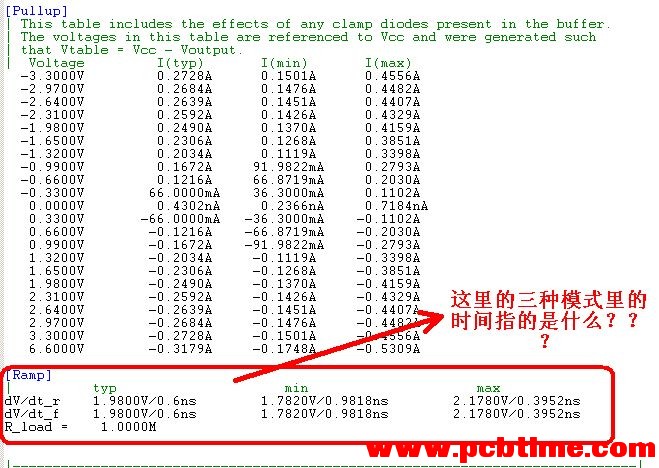

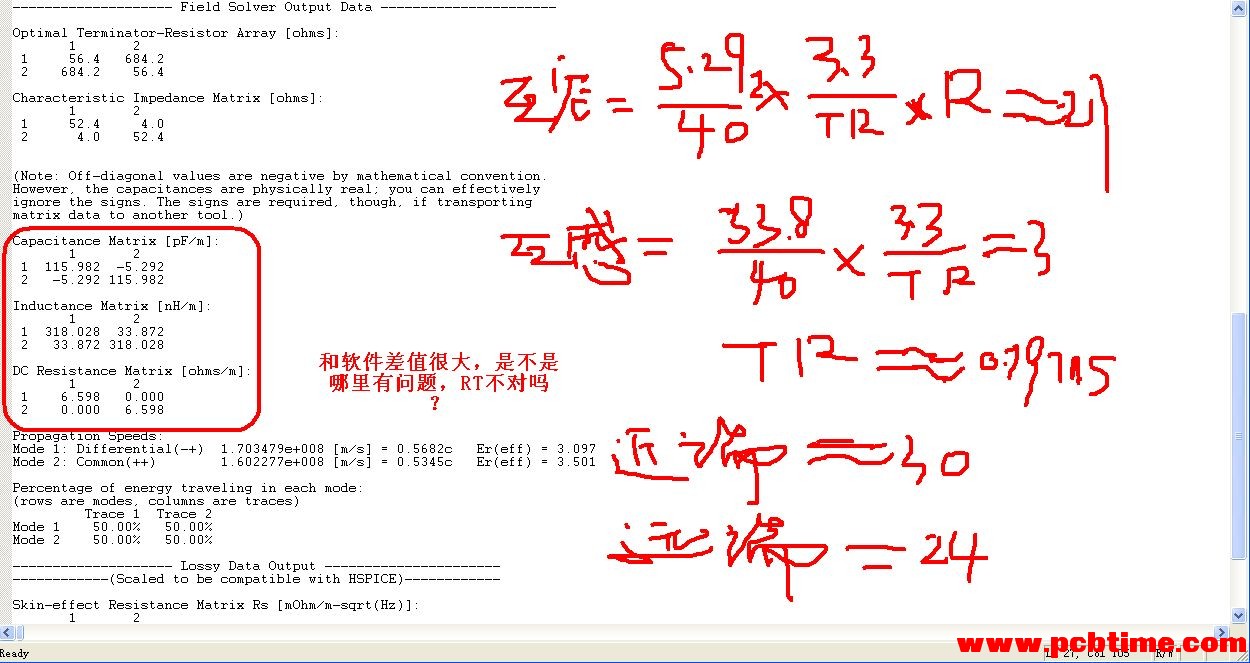

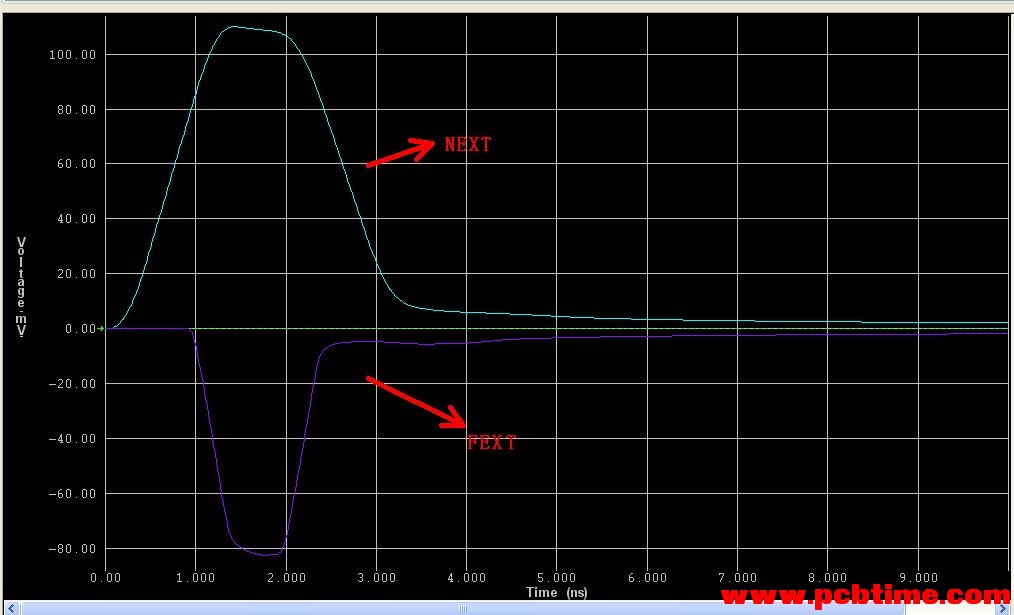

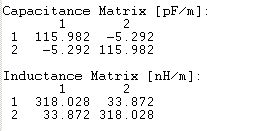

麻烦老师现在看一下,这个建的模型有问题没有,提取的电容和电感参数在下面,近端和远端的波形如下图,随便问一下信号上升沿的时间是怎样得到的,怎样理解仿真这个例子中微带线的远端窜扰在上升沿是为负值?1G 的信号上升沿时间是多少,怎样算出来的,谢谢您

1.关于上升沿的时间,大部分情况下是指信号幅值的10%-90%的时间,如一个1V的信号,上升时间是指信号从0.1-0.9V所需要的时间。在有些情况下上升时间指的也可能是20%-80%的时间,严谨的文档会标注出来。

2.我们知道两条线靠近时,如果A线有从左到右的电流流过,B线上会产生从右到左的感应电流,这个反向的电流在V/T坐标系中表现出来的就是一个负的电压。

可以这么去理解远端串扰这个负的是什么意思。

3.经验公式是上升时间是十分之一的信号周期。实际的上升时间的话还是看芯片模型或者信号协议上的规范吧。像DDR3的上升时间在90-110ps左右。

为什么计算出来的数值与软件仿真出来的差别很大,是哪里出了问题,帮忙看一下,谢谢