辣么纠结,你的AC耦合电容放驱动端好还是接收端好呢?

作者:王萍 一博科技高速先生团队成员

经常有设计工程师纠结着,串行链路中的外接AC耦合电容放驱动端还是接收端好?接2个会有什么影响啊?

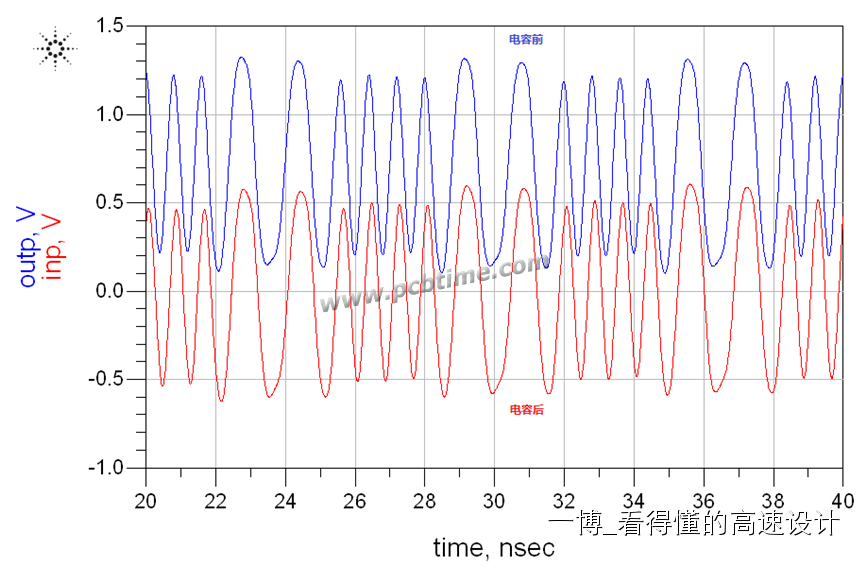

我们首先从ac耦合电容的作用切入。一般使用AC耦合电容是为了提供直流偏压。直流偏压就是滤除信号的直流分量,使信号关于0轴对称。

从这个作用看,其实理想电容应该可以放在通道的任何一个地方。做过仿真的工程师也发现仿真结果确实如此。

可是实际电路中的电容并非理想的,有寄生电感的存在,而且焊盘和换层过孔都是阻抗不连续点。那么非理想电容带到仿真里,电容的位置也没有影响吗?我们用2.5G信号来仿真,全通道长度5500mil,ac耦合电容分别距离驱动端和接收端500mil。

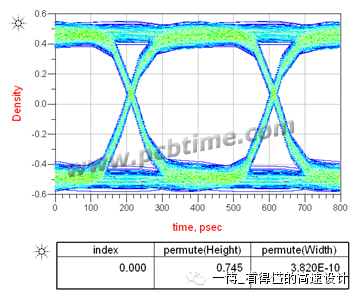

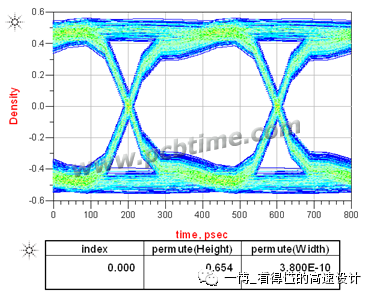

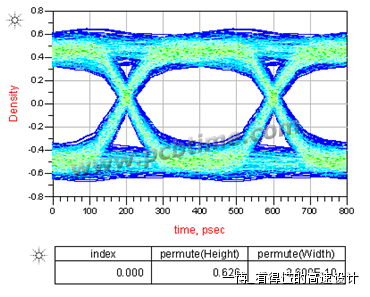

上图是电容靠近接收端,下图是靠近发送端,显然电容靠近接收端眼图质量更好。为什么呢?个人认为可以将非理想电容看成一个阻抗不连续点,如果靠近接收端放,相同的反射系数下,信号经过通道衰减之后再反射会比一开始就反射的能量小。所以大多数的串行链路都要求靠接收端放。

有人又问了,可是为什么PCIE是要求放发送端啊?其实仔细看PCIE规范是说如果是两块板连接时,要发在发送的那块板上。如果发送接收在同一块板上,那么就随意吧。

AC耦合电容还有另外一个作用,就是提供过电压保护。所以更多的要求是靠近连接器放置,USB, SATA都是这么要求的。

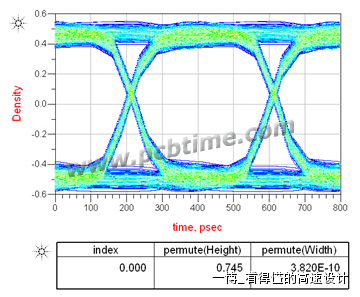

如果通道中接2个AC耦合电容又会怎样呢?

上图是一个电容,而下图接了两个。明显眼图margin变小了,这也是由于多了一个阻抗不连续点,引起了不必要的反射。

最后,总结一下ac耦合电容摆放注意事项:

1,按照design guideline要求放置

2,没有guideline,如果是IC到IC,请靠近接收端放置

3,如果是IC到连接器,请靠近连接器放置

4,尽可能选择小的封装尺寸,减小阻抗不连续

?

***************************

关注高速先生微信公众号:一博_看得懂的高速设计 或扫描以下二维码

把高速设计掌上图书馆装进您的微信

请教几个问题:

1、"如果靠近接收端放,相同的反射系数下,信号经过通道衰减之后再反射会比一开始就反射的能量小。所以大多数的串行链路都要求靠接收端放。" 这个是什么逻辑?为什么发射的能量小就可以放在接收端呢?

2、“明显眼图margin变小了,这也是由于多了一个阻抗不连续点,引起了不必要的反射。”反射和眼高有什么必然的联系么?

新手入门,问题多多,请见谅