PCB设计中关于反射的那些事(4-路的反射)

作者:陈德恒 一博科技高速先生团队成员

文章未动,公式先行:

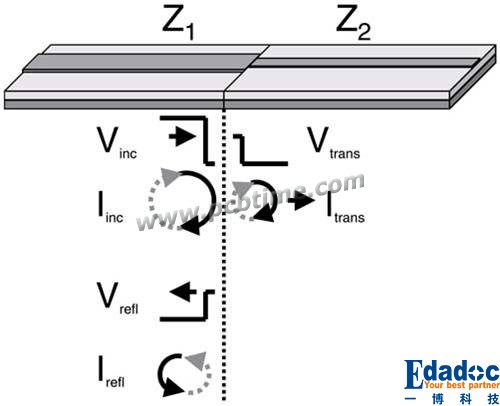

inc ──入射 trans ──传输 refl── 反射

当信号穿越阻抗不连续的点时,会产生反射电压与电流,从而使得分界面两边的电压和电流相等(基尔霍夫定律)。

这样就有如下公式:

V_inc+V_refl=V_trans I_inc-I_refl=I_trans

其中,由欧姆定律有:

Z_1=V_inc/I_inc Z_1=V_refl/I_refl Z_2=V_trans/I_trans

将基尔霍夫电流定律的电流用V/Z替代后:

V_inc/Z_1 -V_refl/Z_1 =V_trans/Z_2

将V_trans替换后:

V_inc/Z_1 -V_refl/Z_1 =(V_inc+V_refl)/Z_2

由该公式我们可以得出:

反射系数

Γ= V_refl/V_inc =(Z_2-Z_1)/(Z_2+Z_1 )

传输系数

Τ= V_trans/V_inc =(2*Z_2)/(Z_2+Z_1 )

在这里给大家自爆一下高速先生小时候学习过程中做过的笔记:

对于理工科来说,一些从数学上去理解问题的过程是必不可少,也是最直观的。

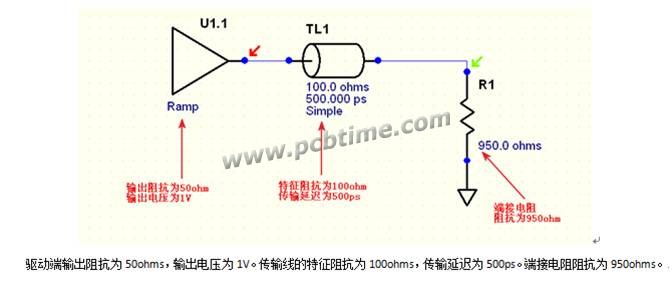

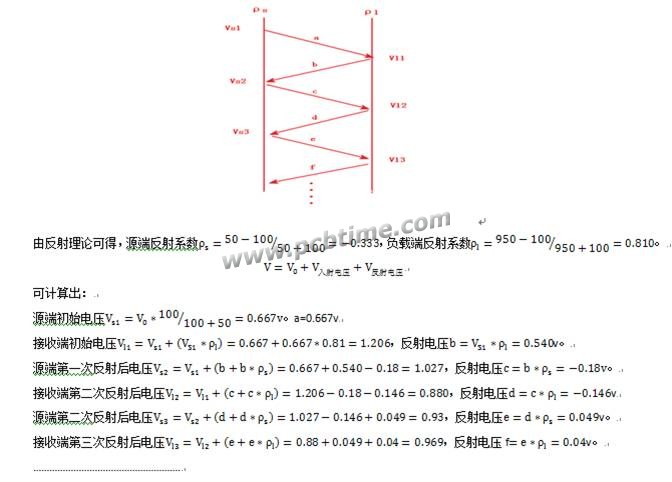

高速先生也和大家一样,学习反射都是从手算反弹图开始的。同样的,小高速先生在画出反弹图之后曾经觉得自己懂反射了。

可是转念一想,还是发现了很多无法理解的问题:

为什么测试时在通道中间测试到的波形有回沟,而在终端测试到的波形又是好的?

Breakout区域有一次阻抗不连续,但走出该区域之后,走线从细变宽,会增加一次反射,那是不是全程按照breakout区域走线会比较好?源端匹配电阻是不是也增加了一次反射?

是的,其实这些用一句“传输线很短的时候反射掩盖在上升沿中了”就可以解释。但是到底是怎么掩盖在上升沿中的?

我们发现在上方的反弹图中传输延时远远大于信号的上升时间,在计算反射时我们用的电压实际上是信号高电平的电压,并没有关注上升沿过程中其他电平的状态,但实际上的情况并不是这样,可是如果我们如果把上升沿的状态加入算式中,那这游戏可就没法玩了。

所以,我们需要场的思维,请看下集分解。

请问,反射系数推导过程中,传输电流等于入射电流减去反射电流,为何电压却是相加?可有详解?

V_inc+V_refl=V_trans I_inc-I_refl=I_trans