PCB设计中关于反射的那些事 (7-深入反射)

作者:陈德恒 一博科技高速先生团队成员

问:穷人思维和富人思维有什么区别?

答:我拿到一2.4mm的20层板给它的28G信号通道做优化,将信号安排在最后几层,花了很久的时间在孔径,pad,antipad,taper,孔距,地孔数量上做平衡,在最后为20mil长的stub需不需要背钻做整体评估时,客户拍拍我的肩膀说:“小陈呐,别那么麻烦了,用镭射孔走第三层嘛,过孔短,stub也短”。

真实故事改编,逗大家一乐。

回顾上一期问题,平时大家想到减小反射的方法大多在匹配传输线阻抗,源端串阻,末端端接,进一步的还有容性负载补偿。

除了减小反射本身,是否还有别的方法呢?有,避开谐振点。

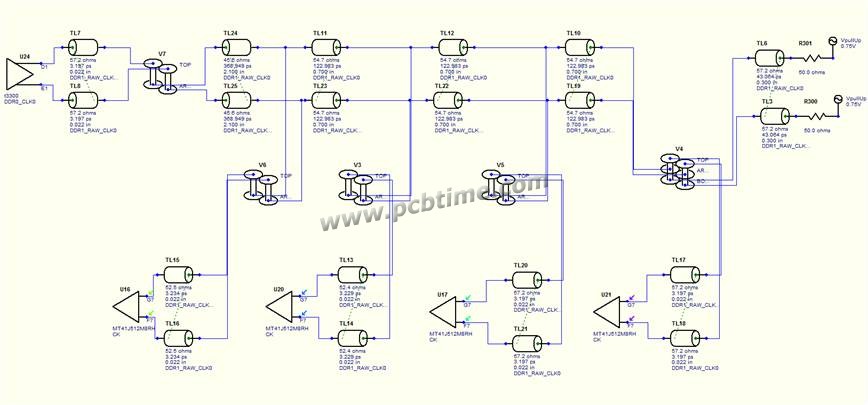

下面是一个简单的DDR3时钟一驱四的拓扑,时钟频率为500MHz:

CPU到第一片颗粒长度为1500mil,颗粒与颗粒之间的长度为500mil,这时接收颗粒的波形如下:

拓扑没有没有问题,末端也用匹配电阻上拉了,负载也并不多,为什么裕量那么小?

回想一下前几节说的,500HMz的时钟信号频域分量主要在500MHz,1.5GHz,这几个频率分量的四分之一波长分别为3000mil,1000mil。而我们当前拓扑中两两之间1500mil,500mil的线长很容易就凑成了四分之一波长,谐振最严重的长度。

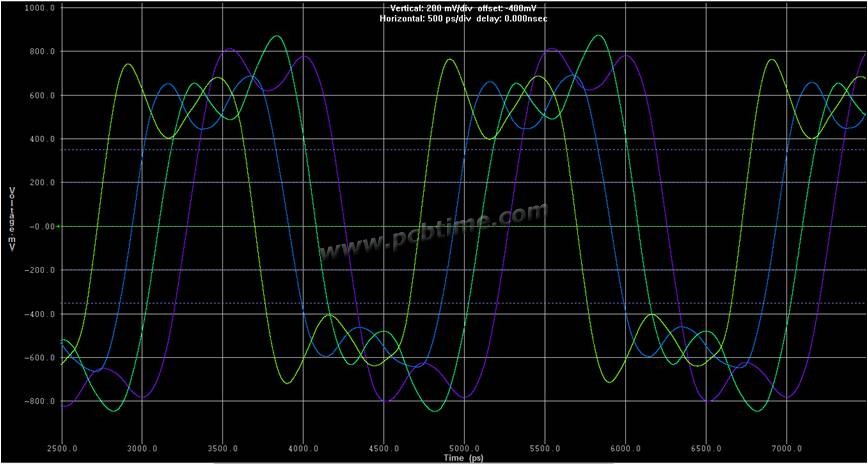

怎么办呢?我们将CPU到第一片颗粒之间的线长延长至2100mil,颗粒之间线长延长至700mil之后:

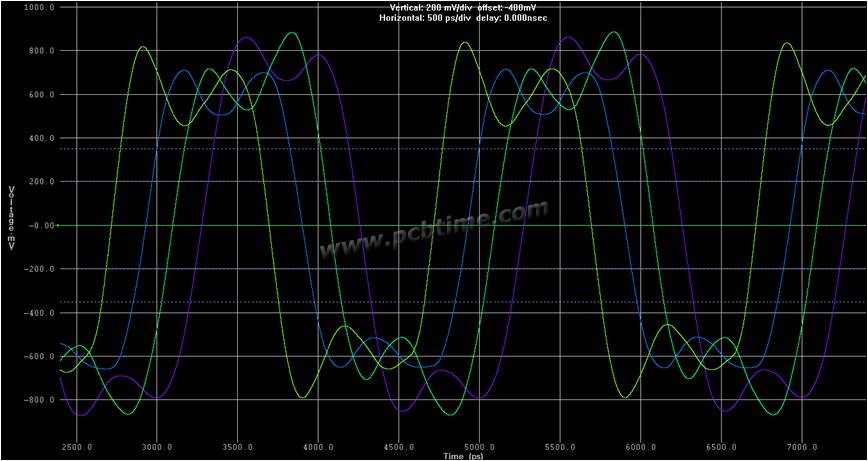

整体的裕量变大了,如果再稍微做一些容性负载补偿:

裕量进一步提升。实际操作时只需要在布局时稍微注意一下器件之间的距离,不需要增加成本,也不需要多余的绕线。

高速先生反射系列的文章到这里就结束了,最后总结一下:

? 反射的本质是波的反射,以及不同相位的波之间的叠加。

? 反射影响的严重程度主要是以下两点:

– 1.阻抗不匹配程度,影响谐振幅值。阻抗越不匹配,谐振幅度越大。

– 2.阻抗不匹配长度,影响谐振频率,不匹配长度越长,谐振频率越低。

? 需要根据实际情况分析反射的影响,对症下药。

希望这一系列文章对大家有帮助,欢迎大家提问讨论。

信号裕量怎么看?没看懂怎么算增加了

图中有两条虚线,在这张图里面是±375mV的样子。这两条线是信号的判定电平,离这个电平越远裕量越大

感谢小编!

你好,高速先生,您在文章中提到四分之一波长形成谐振的问题,我有个疑问,这个应该是形成驻波,导致能量无法传播,这个首先要有反射才能形成驻波,可是在末端已经进行了戴维南端接,消除了反射,怎么还会有这个四分之一波长的问题?希望告诉先生解释一下,上次问了个问题就没有回复,希望这次能解答一下疑惑

不知道你说的是哪一个拓扑,如果是第七章的这个一区四拓扑的话,这只是一个普通的末端并联端接。

确实是形成了驻波使得能量无法传输,实际上这个一驱多的拓扑信号在各个节点都会反射,末端的端接也只能端接掉一部分的反射。