分數型PLL 除法器相關問題詢問(無法懸賞 但我願意付上我所有資產)

时间:10-02

整理:3721RD

点击:

最近在做分數型PLL但是一直鎖不住在這邊推論原因應該是除頻器(Divider)的問題

但是一直找不到原因所以上來求助大神希望能解惑

使用上分數型除數整數N=5

而SDM採用的架構為Mesh 1-1-1的架構

所以除數範圍為2~9

因為一直無法鎖住所以嘗試了幾種不同架構的除法器

而架構圖如下

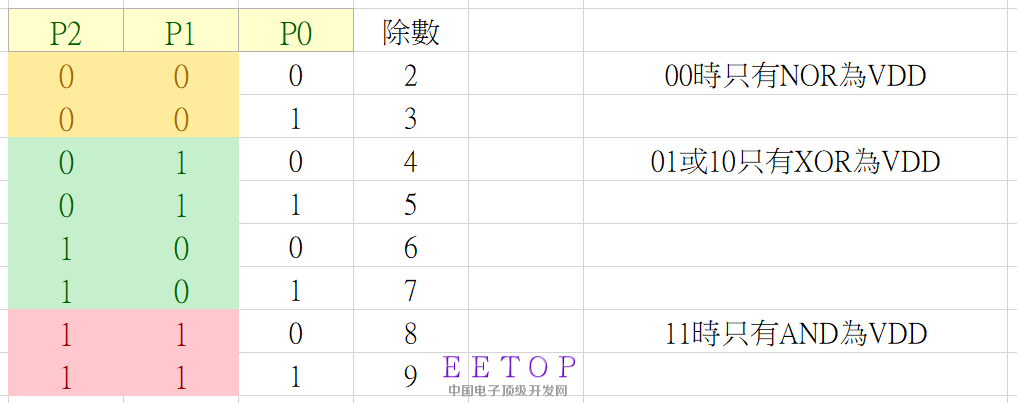

上面的使用原則就是

OUTPUT用AND邏輯閘去做選擇要除23 除4567或除89

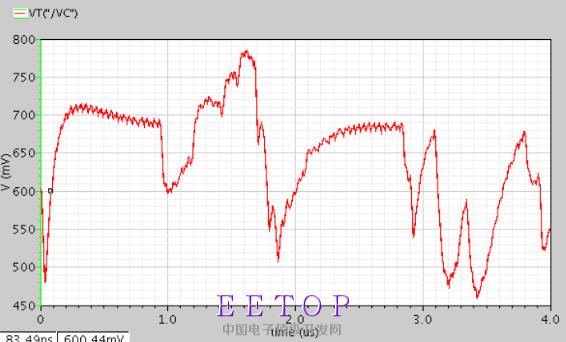

但最後都會鎖不住模擬的Vctrl如下

在設計的時候希望Vctrl鎖定在0.68V

而每次在快要鎖住時都會失鎖

而最後都是在除完8時會發生錯誤

像是希望他除8但是卻是除7甚至除6的波型

希望各位能給點意見

或是另一種除2到除9的除法器架構謝謝

先check各控制字下的分频比是否正确、SDM功能是否正确,再确认二者的timing是否合适。