图中是EN输入ESD结构,求高手指点,谢谢!

时间:10-02

整理:3721RD

点击:

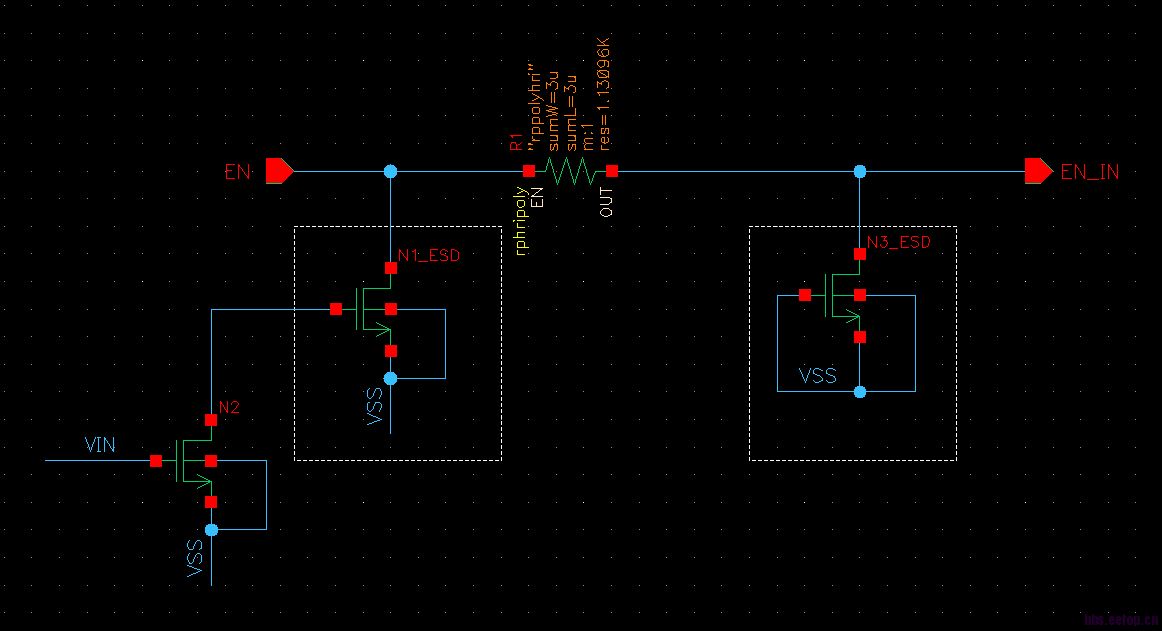

图中是一个0.5um tripple well cmos工艺的EN输入的ESD结构,用来过ESD 2kV,电路如图所示

N1 N2和N3用的是普通5V NMOS管子还是特殊的管子啊? 其W/L大小,漏极面积和layout等怎么确

定啊? 是代工厂给出的还是自己画的啊?

还有,测ESD的时候,是VIN和VSS都接地吗;

还是VIN接5V,VSS接地;

或者VIN悬空,VSS接地啊? 这个电路的工作原理是怎样的啊?请高手指点,谢谢!

这是一种最普通的2级 ESD结构,VIN接的那个NMOS管起到电阻的作用,电路实质是接地,你可以看成GGNMOS的NMOS。

电路的功能是寄生NPN管崩溃导通,泄放电流。

至于第一个NMOS管的GATE不直接接地或接个小电阻,是为了防止N1 不均匀导通失效。

这个是典型的floating gate 的ESD结构,其原理是这ESD event的瞬间使N1走过一定的电流从而触发寄生的NPN的base出现漏电,NPN的base电位可以抬升最后使得NPN管导通。需要控制的是这个电流,小了触发NPN不容易,大了会使得poly gate出现热电子击穿。

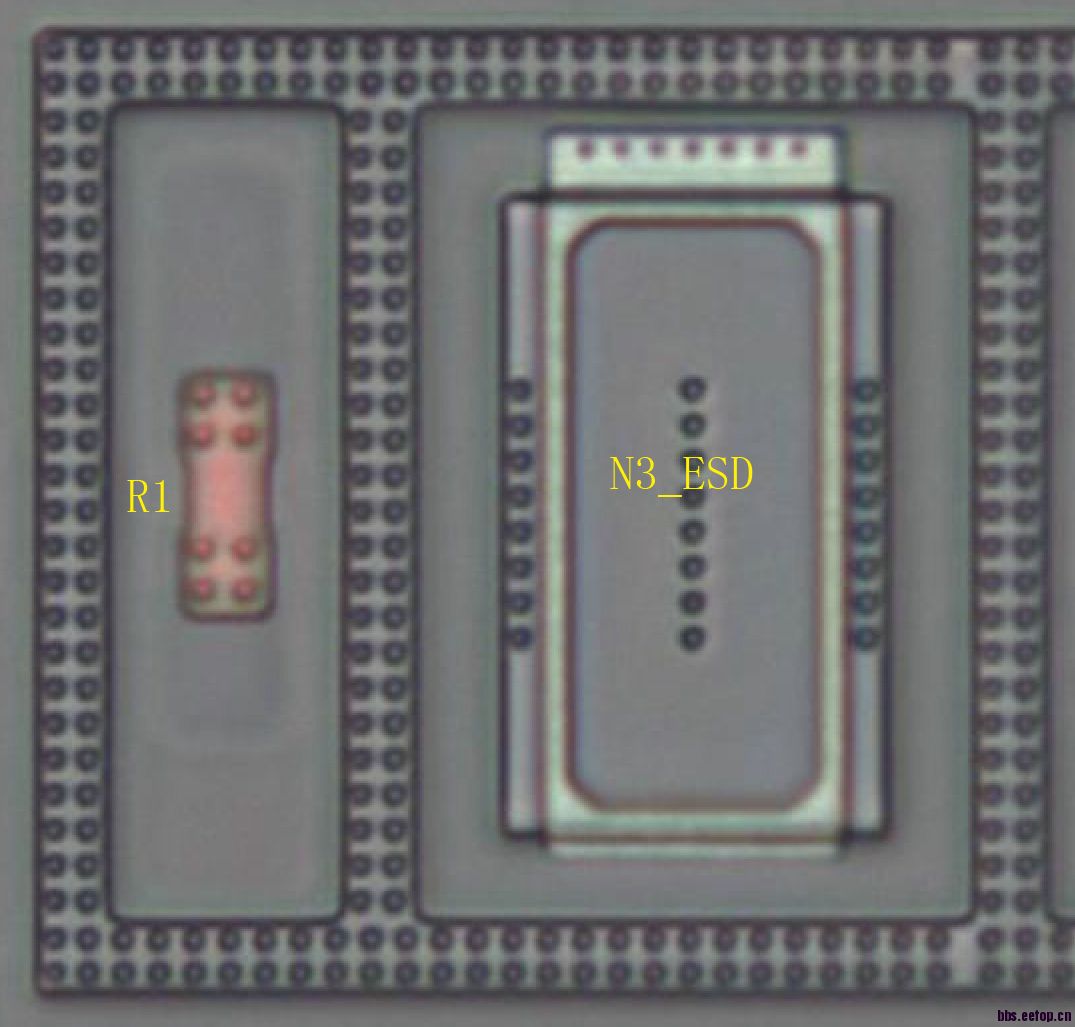

谢谢!查了下资料

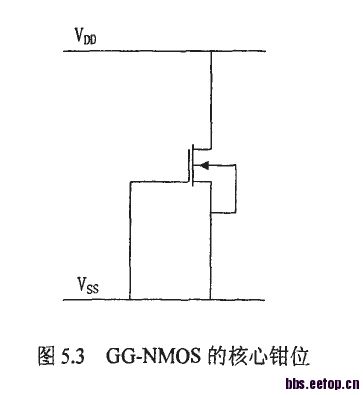

在CMOS工艺中,MOSFET型的ESD电源钳位在芯片设计中已成为一种标

准的ESD设计实现。在早期的实现方式中,一个大尺寸的栅接地(Gate.Ground)

的NMOS管(GG-NMOS)接在芯片的VDD和Vss之间,作为ESD电流的通路,

图GG-NMOS的核心钳位

当ESD发生在VDD与Vss之间时,该NMOS管中寄生的二极管发生回扫击

穿(snapback breakdown),衬底由于调制作用电位上升,引起双极型结构的开启,

VDD上的电压就被钳位在寄生二极管的回扫电压上,从而起到对内部电路的保护作用

谢谢!你的意思是这个ESD的原理是和GG-NMOS是不同的,这里VCC测试的时候是悬空的,所以N1的栅极到地的电阻是非常大的,相当于悬空,是吧?

那你VIN接的那个N2管子不用考虑esd吗? VIN的ESD是否会击穿它? 还是它离VIN Pin已经很远了 不用考虑?

VIN就是LDO的VCC,这里离VIN的焊盘也有个100um远

学习,看看。

您好,能不能把您的ESD结构的资料我给一些啊,我最近也在找这方面的东西

学习了

xuexi。

论坛上就有,找找就行了,我了解得也不多

好的,我下了一些,就想了解一下,对这些还不怎么了解

再来学习一下,现在能懂一些了

学习了