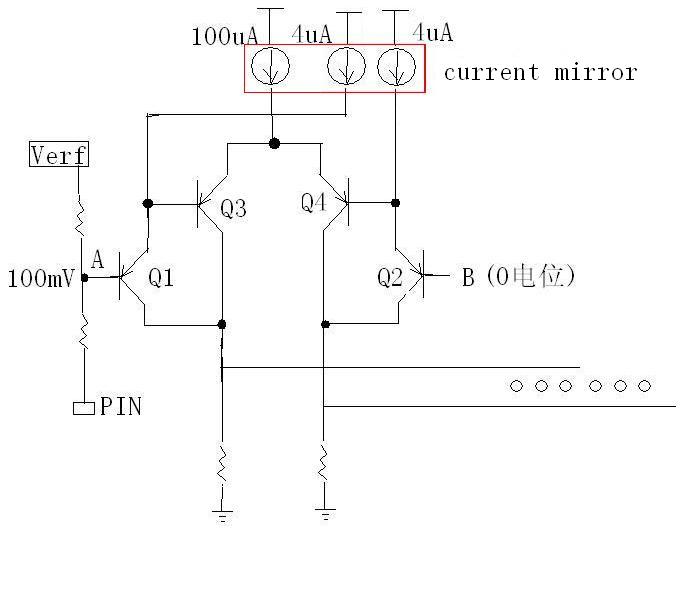

大家看看这个运放的输入结构,困惑.

问题是,Q1,Q2的集电极为何要接到Q3,Q4的集电极上呢? 这样做有什么特别的考虑吗?我认为Q1,Q2仅仅起level shift作用,其集电极可以与地相接.

输出电流具体指哪个电流呢?

有正反馈的作用吗?也就是一旦左侧电位低,输出电流增加的快一点,没有整体电路,不好下结论

看着有点像达林顿结构,不过那是输出用的

好象还见到过一种,差不多的,好象是减小输入电流,减小mismatch current的

至于为什么两个集电极接到一起,因该是接到一起,gm更大吧,充分利用电流咯

我到是见过 两对输入分时控制的!

感觉不应该是LEVEL SHIFTER, 因为它们在竞争一个8UA电流.

像是一个正反馈, 而且这电路可能是一个比较器, 这个正反馈也许是用作设置HYSTERYSIS.

hehe how do you know it is a positive feedback? and where is the hysterysis.

level shifter is indispensable, since the input is 100mV and 0V.

If you think it is positive feedback and hysterysis, you must describe it clearly, but not just possible.

100uA is large current, why was it necessary and where was it applied?

看不动图

>>hehe how do you know it is a positive feedback? and where is the hysterysis.4 m' e6 Pv1 Y

>>level shifter is indispensable, since the input is 100mV and 0V.

>>If you think it is positive feedback and hysterysis, you must describe it clearly, but not just possible

抛转引玉, 抛转引玉. 没有LOVEXXNU同学那么自信啊. 但FEEDBACK还是存在的, Q1B->Q1C(Q3C)->Q3E->Q3B->Q1B, 哪位同学帮着推推是哪种反馈.

还要请教

why "level shifter is indispensable, since the input is 100mV and 0V. "

PNP input pair can work at 100mV and 0V, am I wrong?

In addition, I have anther quesiton regarding the circuit itself. Why the base of Q3/Q4 are shorted together? In this case, the current are distribute evenly (50uA) at each transistor. Is that correct? Maybe qwertyIC can clarify this.

该结构为了减小输入偏置电流!

该结构为了减小输入偏置电流!

Q1B->Q1C(Q3C)->Q3E->Q3B->Q1B

我想知道Q3c->Q3E这个传输存在吗? 如果要是我做回路应该不回跨过一个Vce,Q3C的变化并不一定导致Q3E的同样变化,

当然影响肯定是存在的,不过对于设计来讲我想Vce和Vds这种电压应该利用率不高吧,而且bjt的集电极可以拿来做输入

吗?

共享电流应该只是起到一个节约电流的作用吧,

如果直接将0V电压作为输入,的确BJT可以工作,但是输出电压是多少? 电阻上的电压为Vbe-Vce,最多也就是0.6V吧,

限制了输出电压,而且图中输入一个是100mV,一个是0V会导致两边管子同时工作在饱和区而不是线性区,应该起不到比较器或者放大器

的作用吧,只是粗略定性的看了一下,没有太仔细的看 也可能我分析的有错误。

有反饋的

很奇怪

應可起幾個作用

1. 第一級差動對當緩衝buffer, gain=1, 信號放大由第二個差動對負責

2. 第一與第二級形成Darligton差動對, 可以提高整體輸入阻抗, 減少輸入偏流, 降低電流雜訊, 提高電流增益

当一个管子用?

减小输入偏置电流,设定合理的输出电压直流工作点

如果主电路偏置电流过小,则输出静态工作电压太小

如果主电路偏置电流过大,则输入端吸收电流太大,对输入电压造成影响

因此用四个输入管则可以解决两方面的问题

可能是为了减小由于失调引起的误差

您所在的用户组无法下载或查看附件,如何才能赚点钱?