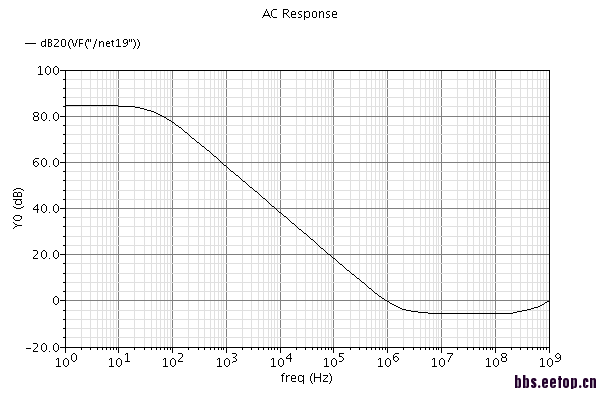

LDO的环路增益有80dB,但是低频PSRR确只有44dB

LDO的环路增益有80dB,但是低频PSRR确只有47dB,PSRR是不是有点太小了?

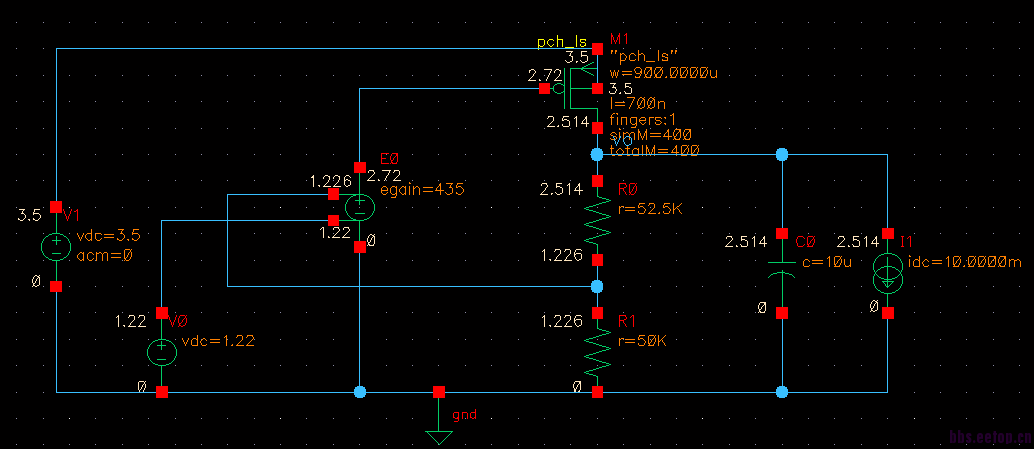

下面是电路图,用了理想的压控电压源做误差放大器,只关心低频的PSRR

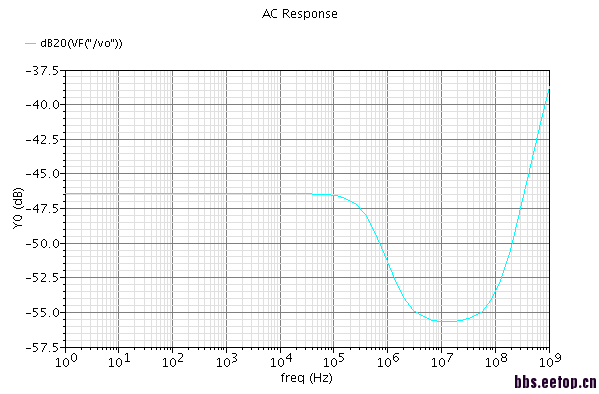

下面是PSRR仿真波形

和增益波形

只关心低频的PSRR

是小了。是否有trimming机制啊?

什么是trimming机制?现在是功能仿真,还没有加入修调电路

仿了下线性调整率约为0.44%

把你的LDO block 贴出来,看看是不是你的环路结构导致PSR偏低。

PSR一般跟结构,补偿方式关系很大,结构不好,怎么调也没用

上图。

LDO在低频时的PSR受LDO结构决定,介于1/beta/Aea和1/beta/Aea/Apower之间(beta:feedback ration, Aea: gain of EA, Apower: power stage gain),理想条件下仿真有可能比环路增益还大!

感谢关注,已上图

感谢关注,已上图

难道是因为我的POWER级的增益太大(40倍),而误差放大器的增益(435倍)太小?

为什么POWER级的增益会影响到低频PSRR呢,它一样的算在环路增益里了?

顶一顶

手算的话低频增益大约在46.5dB,和你的仿真图一致啊?你仿真没错。

这种结构要提高PSR 需要从运放的结构改进

是怎么手算的?

你是用运放的增益和反馈系数来计算的吗,也就是20*log[1/(435/2)],为什么不算上功率级的增益呢?

确切地说是输出级增益除以环路增益。

为什么LDO的低频PSRR是用输出级增益除以环路增益?以前看资料都说是等于环路增益的倒数,也没有看到输出级增益为1的条件

有这方面的资料吗?谢谢

你把小信号图画出来自己推一推吧

对的,就是你的power级的增益太大,power级对于PSRR来说也相当于共栅放大。

在此结构中power级对于PSRR来说相当于共栅放大。

正解!

DCDC是我感兴趣的领域啊。

如何改善PSR在高频的增益呢?我的LDO PSR在高频时出现正值,这是怎么回事儿?