LDO负载跳变太大,怎么办?

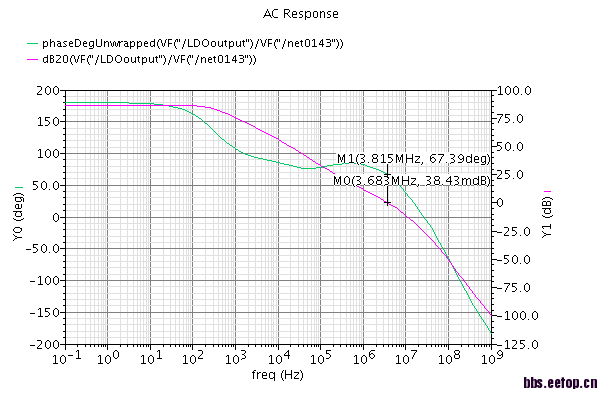

低负载情况下的频率响应

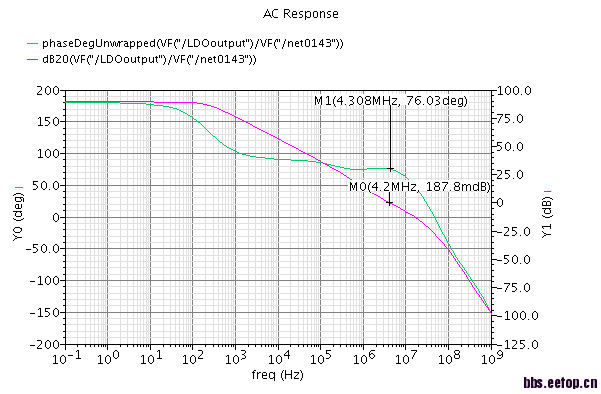

高负载情况下的频率响应

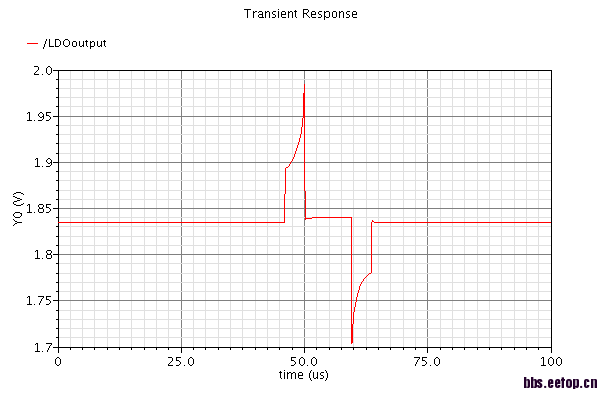

负载电流从500U跳变到50U时的输出

负载电流从500U跳变到50U时的输出

求各位电源高手指点啊

环路的频率响应没加补偿网络就已经够了,但是负载跳变时却有很大的问题,求高手解释啊

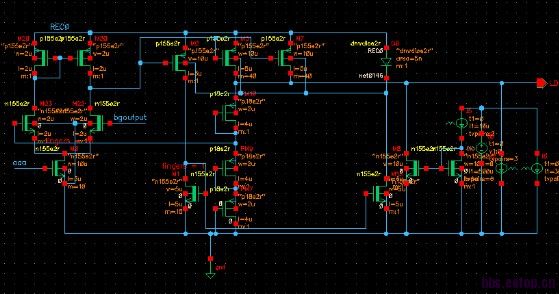

电路图看起来和常用LDO差别蛮大。为啥这样做呢?

仿瞬态跳变大是环路的响应速度不够快,也即是环路带宽不够;而你仿的AC只是基于某一特定直流工作点的交流特性,即使看起来环路特性很好,也只能反映出一个工作点的状态。所以针对LDO更应该注重的是仿真瞬态特性,可以把仿真步长设定在1nv左右,看瞬态时是否会有震荡发生。AC仿真是要保证在最坏状态下环路也能稳定。

其实是个简单的结构,就是在输出那里加了Mora的current boosting的结构,输出的管分成了2个。

负载电流从500uA到50uA就有这么大的变化,确实有些不正常

1. 运放工作电流是不是有点小,导致slewrate太小

2. 没有看到有内部补偿,是用外部补偿的吗?外部补偿的话,电路中最好加上电容的寄生电阻

3. 分压电路用的是pmos,确认一下这条支路的电流,不要太小。提高分压电路的响应,可以在最上面的pmos上并联一个pf量级的电容试试

从你的仿真结果来看是因为你没有输出电容,导致负载下跳很多。你没有标出尾电流的大小,但似乎你的SR不够。其实仿真结果问题很容易找的,看看各点波形就很容易定位问题了。

此外你的diode是为了减小pass device阈值的吗?如果这样做会很危险的。

请问下这样做的话,会出现什么坏的情况呢?

我加上去的时候出现了衬底漏电流的情况,后来问我师兄,他说每个管子都会有点漏电流,然后我就没怎么重视了,还望多多请教啊

这要看你需要什么样的指标了,电路不一定要性能越高越好,满足要求就可以了。

衬底电流有多大?Pass Device也不能超过几百纳。采用把井电压降下来降低阈值的做法是不可取的。

有20几纳,有2个输出管,请教一下,我的输出负载跳变仍然不好,请问是什么情况啊?

学习了……