LDO 的 PSRR 大于0dB

时间:10-02

整理:3721RD

点击:

Hello,

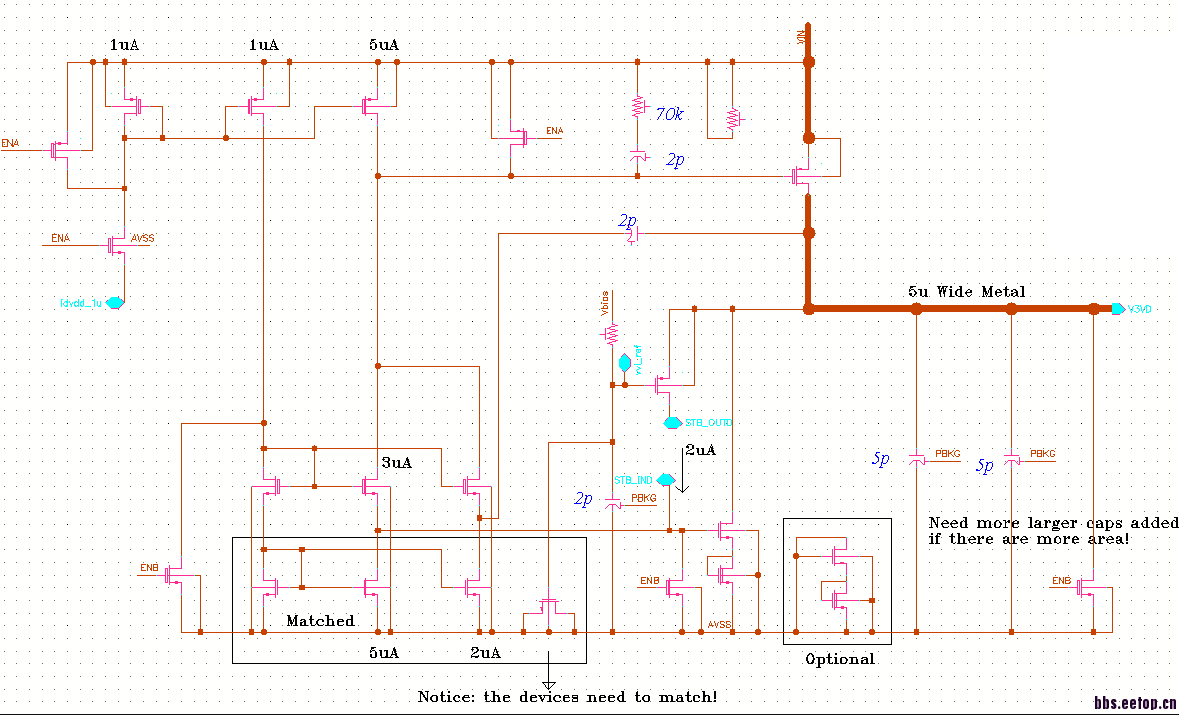

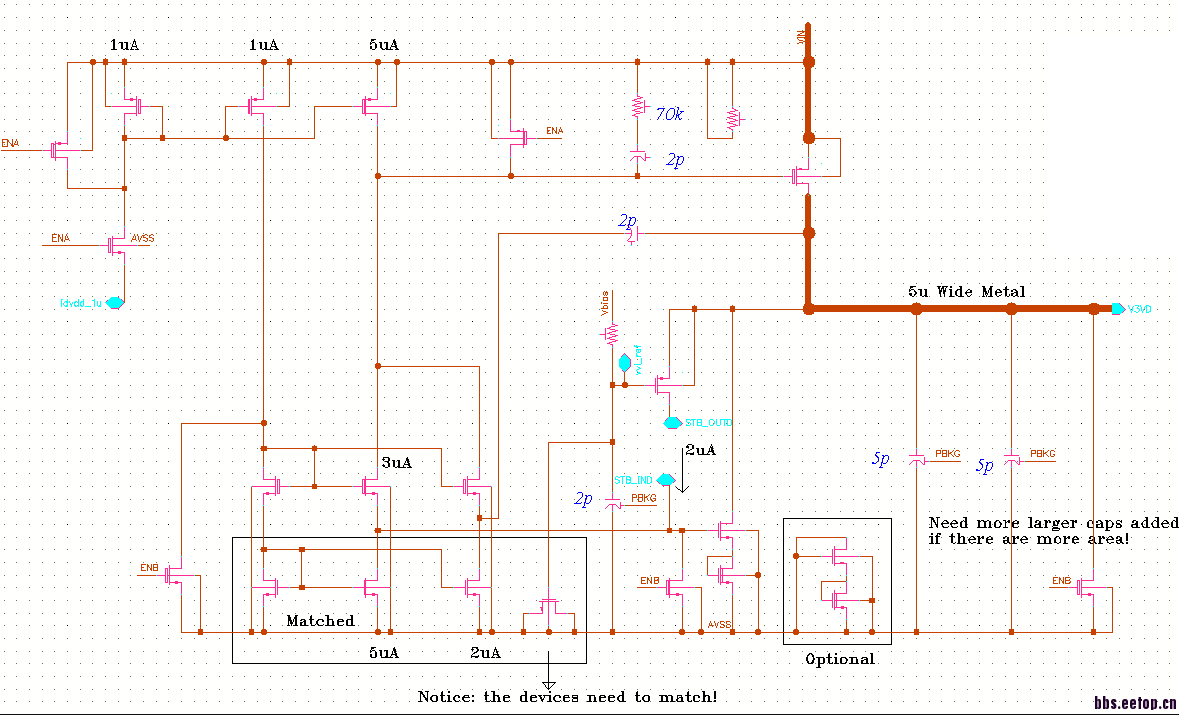

最近做了个LDO,性能还可以,唯有PSRR特别差,甚至》0dB,大牛们看看电路的有什么问题?

怎么提高PSRR,当然我们可以加大输出电容,或者扩展环路的带宽,但是不知道有没有其他的方法呢?

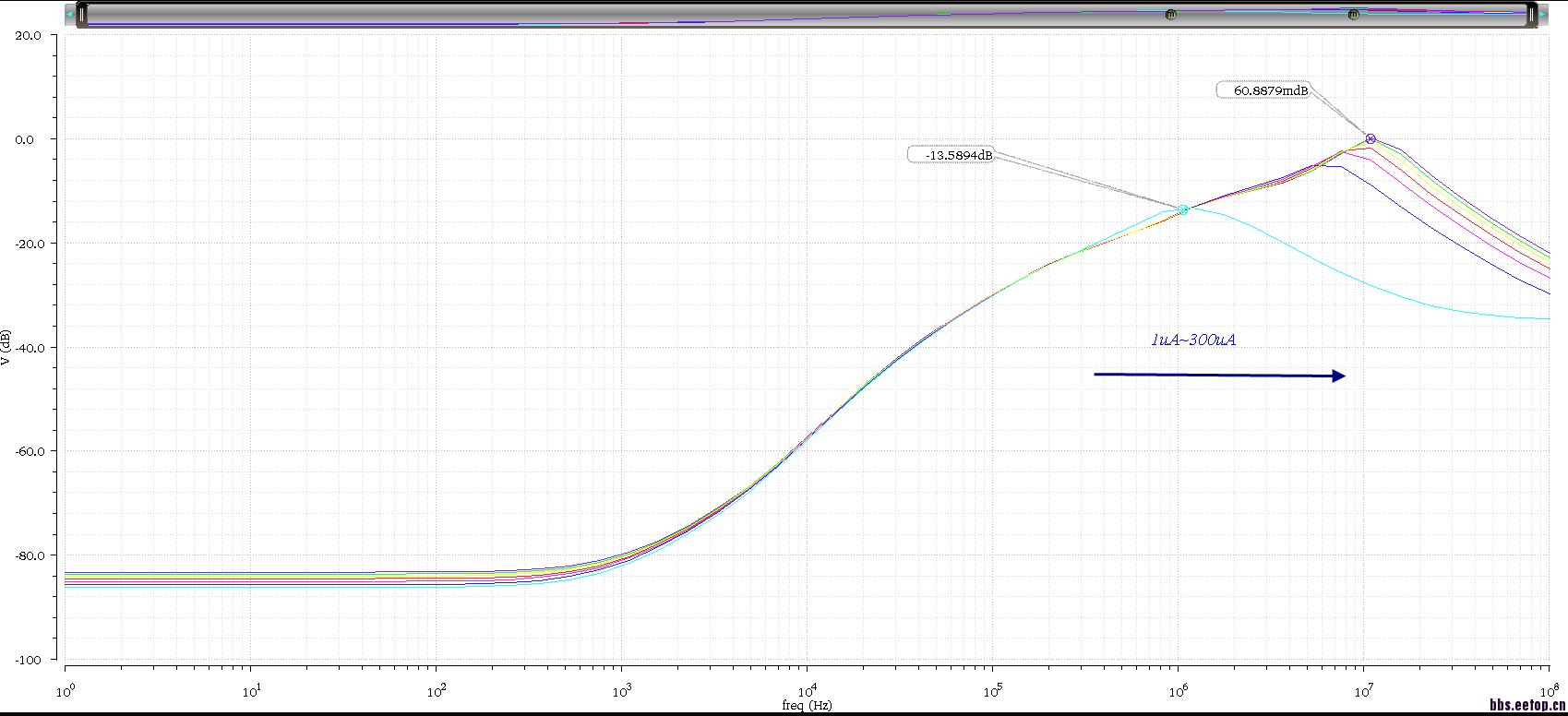

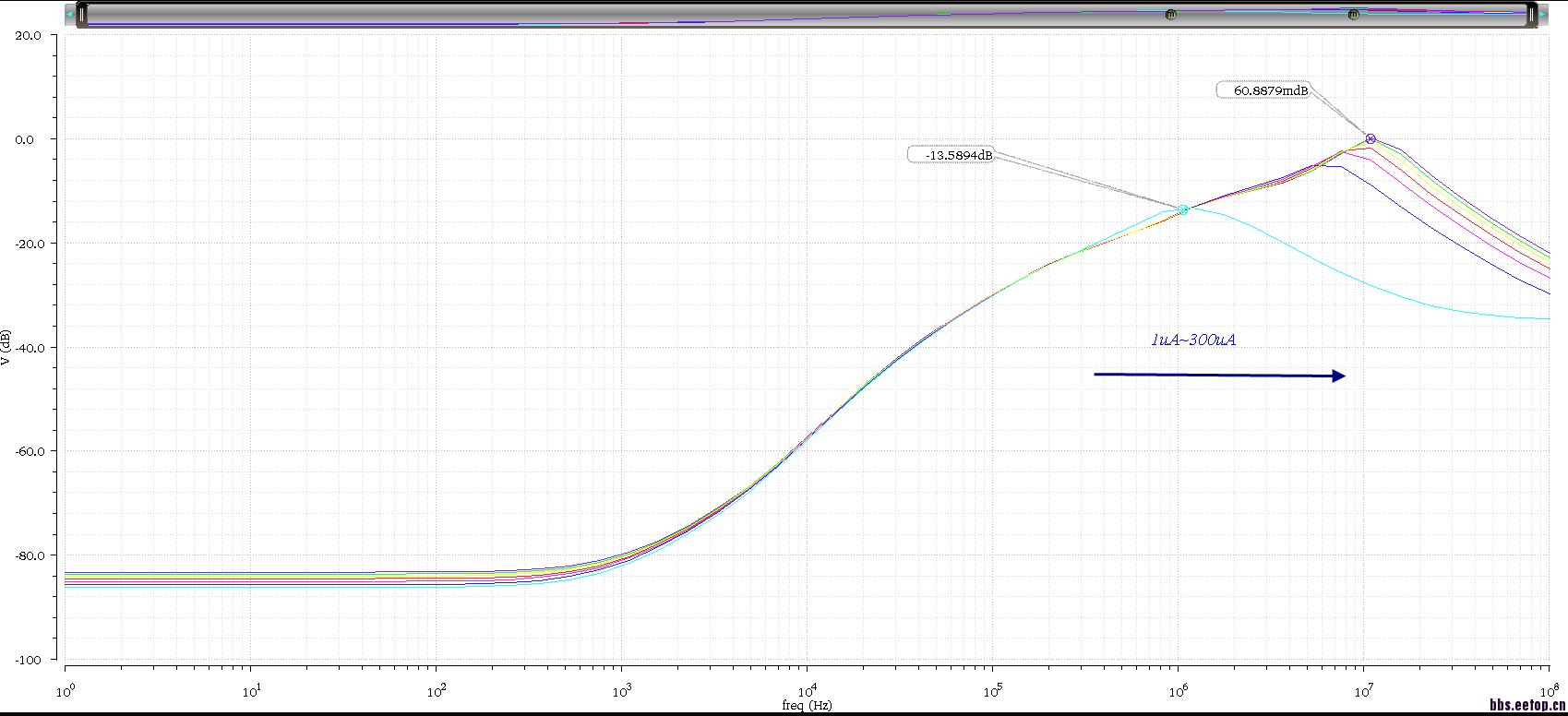

PSRR的仿真

最近做了个LDO,性能还可以,唯有PSRR特别差,甚至》0dB,大牛们看看电路的有什么问题?

怎么提高PSRR,当然我们可以加大输出电容,或者扩展环路的带宽,但是不知道有没有其他的方法呢?

PSRR的仿真

在高频处 馈通

楼上能够讲的详细些,谢谢!

这个电路我没怎么看懂呢,LDO没有运放吗?增加cascode结构,加大运放的带宽都可以增强PSRR吧

this is LDO?!

这个是LDO呀,采用的是单端放大器(共栅级折叠运放),miller-调零补偿;

就是输出电压的精度似乎控制不住,全工艺角偏差个200mV都是小case;

vbias应该特殊设计可以抵消工艺偏差,电流源偏置pmos提供的偏置。

psr大于1的问题是对应频率,已经在GBW以外了,而电容的优化效果还没有产生导致的

你这个VREF输入和LDO_out Feeback在哪里啊?怎么也应该有个差分对输入吧?

为什么放大器一定要有差分输入呀,在LNA里为了省功耗,通常是不用差分的。

LZ 解决这个问题了吗?我先在LDO的psrr在高频出也出现了》0dB的值,这个要怎么解决呢?