Bandgap+Comp结构POR

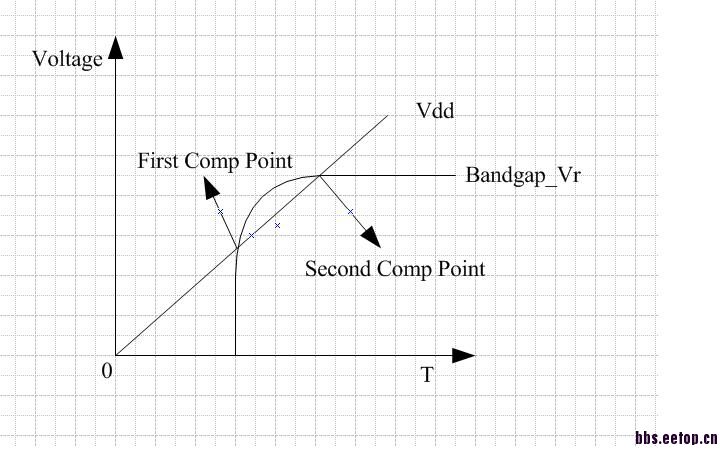

最近搞一个Bandgap+Comp结构的POR,但是在VDD上电过程中,会出现两次和基准电压相等的点,直接导致出现两次复位信号。

不晓得这个是这种架构的缺点还是有什么方法可以解决掉的?

我有一个不改变构架的解决办法:在比较器后面加个固定时间的延时,保证延时在任何条件下大于first comp point 与second comp point之间的时间差。

你把逻辑反过来不就是一次复位信号了么。如果这样复位时电源不够,就把bg的vdd连到你图上的这条vdd上,就不会有交叉的情况出现了

但是VDD的上电时间不定,所以first point 和second point 的时间差也不固定,如何设计比较器的延迟能够保证10uS到1S之间上电都不会出现呢?

没搞懂你Vbg电压为何会高于vdd电压,难道bandgap用的电源不是vdd?

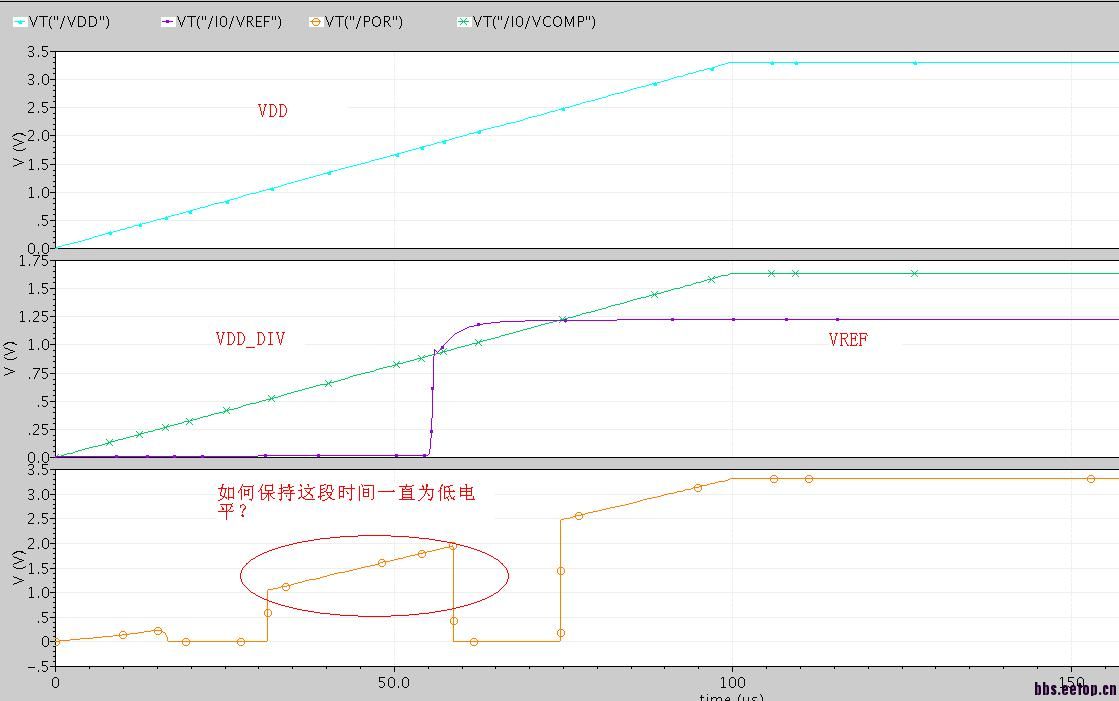

可能刚才说错了,贴了个图,你看看如何消除前面一段时间的高电平。VDD:电源VDD_div:VDD的电阻分压信号VREF:基准POR:复位信号

那你这样做:当电源电压到1.6V左右时候,基准就可以正常工作了,这时基准从0快速变到1.2V,但电源分压的VDD_div没有到1.2V。那么你要做的就是增大基准电路的最小工作电压(所有条件下,基准电路的最小工作电压VDDmin/电源分压比>基准电压1.2)。

否则就是更改por构建。

搞错了,。

因为基准的工作电压比较低

恩,非常感谢啊。

这个基本不可能实现。

真没遇到过

不知道你说的什么不能实现?

VDD_div不要直接从VDD分压,而是串一个开关,这个开关由Vbg控制导通。

初始时开关断掉,VDD_div为0,当Vbg足够高时才导通开关,VDD_div升高。

为增加可靠性,还可以将VDD_div通过RC延迟后再用于比较。

用bgr的输出VREF去控制一个翻转阈值大概在0.6V-1.2V的反相器,然后用这个反相器的输出与比较器的输出做逻辑与,产生所需要的POR信号、

14、15楼建议的方法比较好,也是比较常用的。

学习学习

顺便问问,这个bgap在vdd上升过程中,可能会oscilate,如果用到opamp的话。是不是应当用mirror的,不用opamp?