请教common-mode feedback的问题

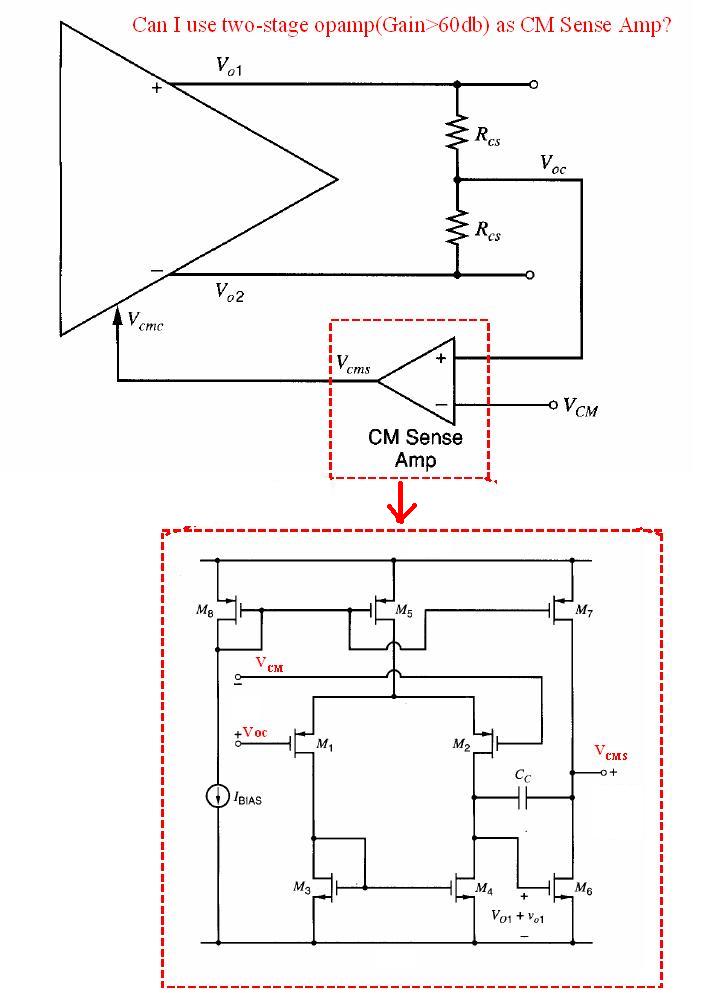

我是否可以用一个two-stage cmos OP (gain >60db)做为differential-input and differential output op amp的 cm sense amplifier?Please explain it.Thanks you in advance.

Paul Gray page 824 Figure 12.16

没有任何别的要求的前提下,当然可以做(当然cm反馈回路要稳定)。

但稳定只是说整个电路静态时Voc是在Vcm的。

实际中cmfb的目的往往是希望动态时(即查分电路在大幅工作),Voc能维持在Vcm附近缓慢变化而不是跳动。

这就要求cmfb回路的主极点(即变化最慢的点)在Voc,而不是你现在电路这样在M6的gate.

你仿一仿主极点在不同位置时的瞬态就看的到差别了。

我的理解是,如果你看整个CMFB loop的单位增益频率,这个值是Acm*gm/C, Acm是CM loop的dc增益,gm/c是环路主极点位置(暂时不考虑在主放大器输出端还是CM sense amp内部,但是假设整个环路是single pole roll off)。如果你的cmfb放大器增益太大,那么这个单位增益频率也很大, 这样就会有更多的非主极点进入cmfb 带宽内,从而导致环路不稳定,这也是为什么通常cmfb sense放大器只用简单的diode负载的原因;

至于环路主极点的位置,我觉得理论上在哪都可以,之所以放到输出端,是因为这个地方也是主放大器的主极点,把补偿放到这个位置相当于同时补偿了CMFB和主放大器DM。如果你把主极点放在CM sense amp中(这里不考虑该放大器增益的影响),为了环路稳定,那就要求主放大器输出极点在cmfb loop bandwidth外,但是由于你把这个放大器增益设定的很大, 这样环路的单位增益带宽也比较大(环路有两个增益级,GBW不是固定的),这就要求主放大器的输出极点(假设为主极点)也就要比较大,这就达不到对主放大器进行输出补偿的目的了。通常CMFB环路的单位增益频率可以设定在主放大器单位增益频率内。

其实只要cmfb loop gain足够,并且环路稳定,共模输出电压就和理想值接近。

说的不对的地方还请大侠指出。

3L 说的基本正确,一般情况是不可以的,

CMFB的增益过高会引入一个低频极点导致环路不稳定,

主极点放在输出的一个好处是当驱动负载增大时,不会影响环路稳定,

我觉得,主要问题是CM Sense增益太高,导致cmfb loop的unity gain bandwidth很大,这时cmfb loop中的非主极点会影响cmfb loop的phase margin,容易不稳定。

不过主极点在CM Sense内部的话会是更好的设计。一般来说cmfb loop的unity gain bandwidth比DM loop的要小一些,所以如果主极点在放大器输出的话,在输出端加电容补偿是以cmfb loop的phase margin为标准,可是这时候DM已经overcompensated,会影响放大器的带宽。所以最好把cmfb loop和DM loop的主极点分开。

cm feedback gain is too large

cm loop not easy to stable!

3-5楼的没分清信号通路是差分通路,跟cm通路是相关度很低的通路,怎么能拿cm环路的所谓gain/bandwidth去讨论对差分通路什么极点位置影响。

物理直观上讲,对于主差分op来说,它理想中希望看到的是Rcs电阻连在一个cm的ac ground: Voc!

什么是ac ground? 电压不变的点->缓变的点/电容大的点.

cmfb环路的目的就是让voc成为这样的点,而在任何环路的settling过程中,主极点永远是最稳定的.

如果主极点不在Voc,你就不能在Voc增加电容,让它对主差分通路来说接近ac ground. 这才是cmfb反馈定主极点位置的最重要依据.

如果你不想让Voc成为ac ground,那你就可以任意设cmfb的gain/bandwidth/pole,哪有什么gain太高影响主运放环路的事啊.

看了上面的一些讨论我说一下我的观点, 我觉得只要能保证共模反馈环路的稳定,就可以用LZ说的电路做sensing,但问题是这个稳定不好做。把CM环路和DM环路分开看,这个二级运放内部含有一个高阻节点(M4的漏),它的输入(即主运放的输出)也通常是高阻大电容节点,这样的话这个环路要稳定设计起来就很麻烦,miller补偿可以的话那就补,不能的话也也就只能在M4的漏加一个很大电容,毕竟输出负载电容是多少并不是设计者可以决定的。

所以,我的观点是,不这样做的原因在于CM环路有两个高阻节点,且难以把它们分开。

对于说增益太大导到GBW太大影响稳定性这一说法,嗯,我觉得这里的推理关系我不是太同意,虽然都在说稳定性的问题,因为直流增益的增加不会影响运放的GBW。直流增益上升,-3db BW会下降。GBW保持不变,而且我觉得对于非单极点roll off的系统(这里有两个靠得很近的极点),不能用A*BW作为单位增益的带宽了吧。

连续时间的共模反馈的建立时间太长吧?

还有请问小编,您主运放的输出接口是?源极跟随,还是?

CM和DM有个共同的极点,也就是主放大器输出极点,楼上所说的那个ac ground点,从这点来看也不能是相关度很低的通路了吧;

CM SENSE的增益影响稳定性,简单考虑可以这样看,假设这个sense opamp是个理想的放大器,只有DC gain A0,CM环路增益就是A0*A1(主放大器中的部分的增益);假如那个ac ground点,也就是要稳定的cm点处的极点同样也是cm环路的主极点Po,那么由于这个额外的A0,必然cm通路的GBM要比A1*Po大,为A1*A0*Po;由于CM通路与dm通路相比通常包含更多的极点(比如说如果主放大器是个差分放大器,反馈接到尾电流源,那么尾电流源的漏端就存在非主极点),这个GBW的增加有可能会导致非主极点进入GBW内,从而影响CM环路的稳定性,这样的CM环路不稳定了,DM也就没法正常工作了;

GBW不变也是对单级点系统来说正确,对CM通路来说,它由两部分组成,一个是CM SENSE amp,还有主放大器中可以提供增益的部分,如果cm sense amp增益很高,假设主极点就放在主放大器输出端,那么这个cm sense 的高增益必然会影响cm环路的稳定性。大牛们都来讨论一下吧,集思广益,呵呵

help me, please

ddddddddd

help a lot

谢谢,学习了。

我觉得共模,差模,稳定都没问题的话,这个结构可以用

学习了

果然精辟

要那么大增以何用?

共模反馈环路稳定不了。

搬板凳来听课

说几点我的看法,这个问题其实就是共模环路速度和差模环路速度谁快的问题,首先3到5楼的观点我不认同,这完全是两个不同的环路。其次,两者速度的问题,感觉有比较大的争议,个人偏向共模环路的速度大于差摸为好,比如上电的时候先稳定共模环路,会更利于差模的稳定。这样来看选择的运放要有比较高的单位增益带宽。所以这个运放合理设计没有问题。但个人认为两级有点浪费,只要稳住共摸就好了,单极够了,差分输出的好处就是,可以抵消共模的变化。

難得見到的好帖,好就好在大家這麼積極地在討論,並且分析的有道理有根據。希望自己能夠很快有能力參與這樣的討論。美國又要想辦法抑制中國集成電路設計產業的發展,我們要奮鬥起來,為國內的集成電路產業的成長揮灑汗水。