请教关于sync tip clamp 视频箝位电路

最近要做一个视频箝位电路,有些问题还想请教。

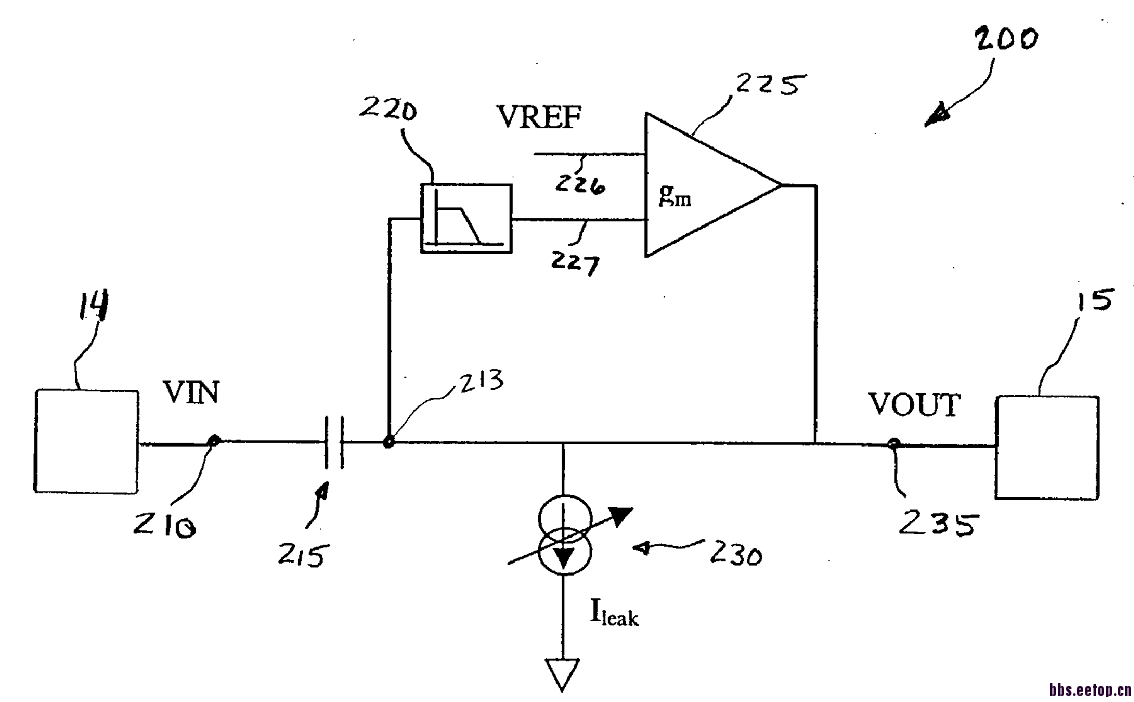

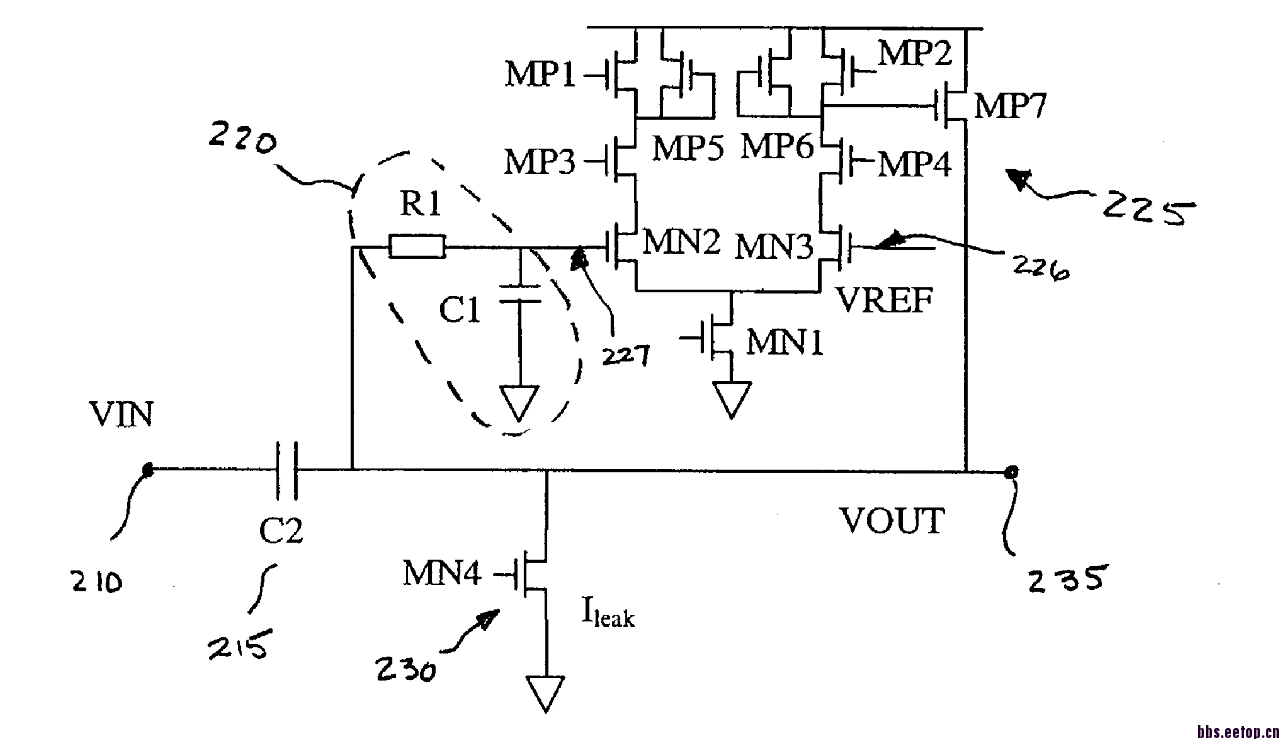

左边是一个专利的视频箝位电路的原理框图,右边是它的具体实现图。

1、视频信号与VREF比较以前要见过一个RC低通滤波网络,我理解的是为了滤除色同步信号和有效视频信号,只留下同步信号,从另外一个专利看到,这个RC的带宽只有300KHz左右,假如C=1pF,那么R=13M。请问在短沟道的CMOS工艺这么低频率的RC滤波能实现吗?怎么实现啊?

2、输入视频信号(CVBS)的幅度大概是-0.3~0.7V,同步头是不经常箝位在0v,那么Vref=0,在上面的电路中,Vref=0似乎不能工作啊?

3、一般sync tip 箝位都有一个Ileak电流,在视频有效图像区仍然在流,这样是不是会影响箝位的精度?sync tip的箝位精度能不能做到10bit?我查找最近的一些论文,目前似乎一般都是采用charge pump clamp结构。

图片挂了

首先想说一下,你show出来的电路是sync tip clamping,其实就是个bottom clamping,因为在电视标准中,sync tip是最低电位,高度大概在300mV,也就是back porch的位置,亮度、色度信号不允许低于back porch,但是会有些非标的情况

(1)R1-C1 filter我猜测有两个作用,一个是滤掉sync tip上高频jitter,另一个就是对应于非标情况,如果有高频色度信号低于back porch,可能会被当做sync,如果加了这个filter,那么把色度信号滤掉了,也不会抓错sync但是这样做的缺点就是,sync的下降沿很慢,产生的latency,在产生pixel clock时候可能要处理这个delay,以前我们并不会加这个filter

(2) video信号是AC couple的,也就是C2,芯片内部是DC 是由设计需要定的,也就是做clamping 电路的原因

(3)关于sync tip clamp需要有个leakage current,由于clamp电路只是一个charge电路,要防止内部信号很高的时候,也要让信号下降回到正常的电平,就需要有个leakage,这个电流可以做的比较小,具体大小需要根据C2很行频计算,比如一行掉2mV或者5mV,这个东西自己定,video不需要10bit精度,人眼没有这么敏感,而且这个是低频,只是亮度稍微变化一点而已

BTW,我已经好多年没做video了,早就跟不上形势了,哈哈

谢谢大神,您当初用的是这种sync tip箝位吗?

再请问Icharge的最大电流是根据什么来选择的呢?

clamp重要的指标有哪一些?

自己顶。

再顶。

再顶。

可不可以问一下这篇专利的链接?

专利可否共享?

哈哈,明白了

為後來人留經驗。這第1點中,RC濾波器的帶寬不該做到300KHz這麼低。sync tip的寬度為四點幾個us,300KHz對應的RC常熟為3.3us,這大概是視頻信號由較高電位降到sync tip的時間,那剩下的來做clamp的時間就很少了,有可能clamp都沒時間做。