关于SAR比较器

SAR比较器

怎么没人回答呀

短接输出可以做 reset,以减少比较器在大信号比较后的恢复时间。

瞬态响应更好。相应提高比较器速度。

谢谢你的解答,你所说的reset具体是什么,为什么能减少比较器在大信号比较后的恢复时间,还有这种比较器的失调应该怎么仿真,谢谢!

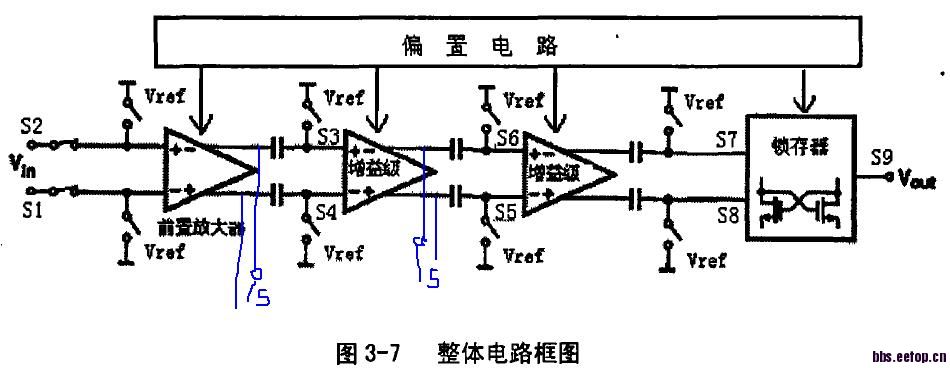

你好,再请教你一个问题,在图中第一级的运放的增益不能太多,否则会使输出端的电容饱和,我不大理解电容饱和是什么意思,你能否给我解释一下,无限感谢!

因为你的opamp会有mismatch,如果不reset的话,就会形成residue,久而久之就饱和咯

所谓的饱和是指什么,不大理解饱和的意思

就是吃过了3碗面条,再也吃不下一个饺子的意思。

饱和就是电容上的电荷越来越多,对应的电压越来越高或越来越低,最终到电源电压或地电平,然后就不会有变化了吧。

对不,jesseyu?

输出短接,泄放电容的残值电荷。你可以把电容看成电源,对两个电容短接,是不需要从op抽取太多的电流的。

饱和的问题: output=Vos*Av 开环情况下,大增益会使 Vos*Av>OP output range (less than VCC) 进入非线性区。

你这个电路是输出offset消除,自己找书看看原理,注意每级之间的时序。时序合理offset是很小的。

offset 仿真可以在输入加三角波信号,做瞬态仿真,看输出的转点,注意ramp的信号斜率。

回答很到位,学习了。

问个问题,offset 仿真还是可以用 monte carlo 吧?

对的,因为你是 clock control comparator, 需要瞬态仿真

非常感谢你的回答,让我受益匪浅,谢谢你!

长见识了同学习

受益匪浅

auto zero

offset cancel?

输出存储型auto zero,用来做offset calibration

学习了

长见识了,学习学习,请问大神们有木有关于如何选取SAR ADC中比较器的资料或者书籍呀,之前我帮老师画过一个SAR ADC的版图,后仿,后来拿去流片了,我对SAR ADC的结构算是有了比较清楚的认识,但是现在我想完全靠自己设计一个,想想前面的基础理论计算,有些还不是很明白。比如比较器的性能得有多少,才能比的出来,还有电容阵列的单位电容选取时候mismatch和KT/C噪声要怎么考虑,或者采样电路的位数是不是不用完全和要达到的位数一样?比如之前我老是设计的那个10位ADC,其实采样只用了9位,但最后出来的结果有效位有9.7。这些我都想全部弄清楚,如果大神们有资料,求共享呀O(∩_∩)O~

learning !

请问一下这种结构的比较器,增益带宽都合适,后面的比较周期共模电平掉的很厉害,是怎么回事