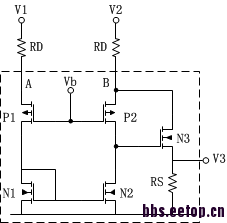

一种common gate的运放电路请教

对于电路的功能比较好分析,检测V1和V2之间的电压差(V2>V1),然后转化为V3输出,关系式为:V3=(V2-V1)*(RS/RD)。

但是这对于设计电路帮助不大,因为没有反应出具体的性能参数。

昨天在分析这个电路时,发现里面包含了一个共栅输入级的差分运放,如图中虚线框所示,输入对为P1/P2,N1/N2做为active load,N3是第二级输出,这一运放构成一个buffer,将A点和B点调整至相等的电位。这一运放的增益也决定了整个电路的精度。

但是分析仅仅进行到这一步,除了精度,其他性能参数很难进行下去。在网上也未搜到关于这一结构的相关资料,不知是否是因为太简单的原因。

所以想请教各位大侠:如果V1/V2端有扰动,会在输出端V3造成相应的扰动,这会造成后续电路误认为所设定的电流值达到而切换芯片的工作状态,最直接的结果是过流保护值偏小,而带不了大电流。这该如何去设计电路?

如果有大侠有关于这一电路或者类似电路的相关资料,望能给小弟分享一下。

在此先谢过各位。

你这个哪里PMOS哪是NMOS?

标题

小编不错,挺爱钻研的!

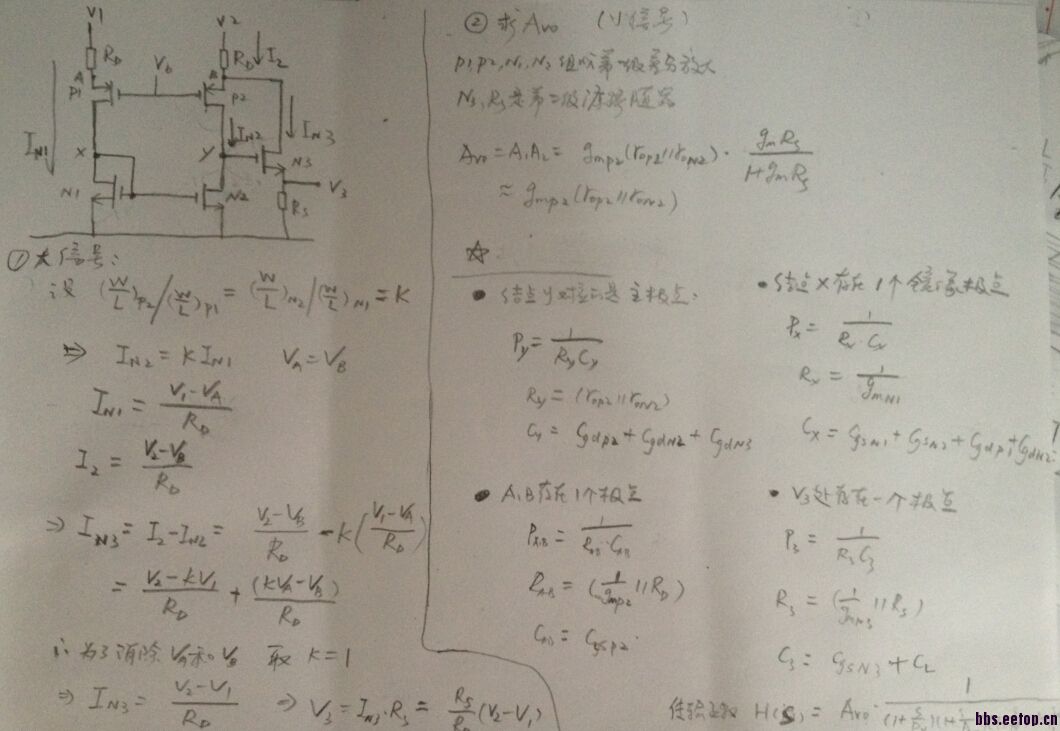

既然基本的情况已经搞懂了,这个时候就应该用一种正向的思维来考虑这个电路的设计了。首先电路的功能是为了实现电流采样,采样无非就是精度和速度,精度和增益有关,速度和带宽有关,把两者式子列出来,看看和每个管子的参数的关系是怎样的。这样就很清晰了,也知道怎么优化电路了。再就是考虑环路稳定性,怎么补偿,最后考虑失调的影响…

具体式子就不列了吧,小编可以把思考的东西再贴出来供大家讨论…

以N开头标注的管子是NMOS,以P开头标注的管子是PMOS。

谢谢这位大侠的回复。对于速度的问题,我的想法是存在一下tradeoff。在采样电流时,V1和V2是连接至采样电阻的两端,而在开关过程中,这两个电压存在高频扰动,如果这个电路的带宽很宽的话,就会响应这些扰动而使后面的电路产生误触发。所以这个tradoff该如何考虑?

另外是N3的drain端直接连接至V2端,V2端的扰动会通过N3的漏源寄生电容传导至它的source端,这也会使电路错误工作,有没有好的办法解决这个问题?

不知道这个分析对不对,贴出来请大家指正

分析得不错。但是对于小信号增益,如果以V3作为输出结点,增益确实为gm2*(rop2||ron2),但是我觉得在设计增益时应该将N3作为共源级,输出点为B点,因为精度是由A点与B点之间的电压有多接近决定。

传输函数和零极点分析我认为也是正确的,但是该如何设计这个电路的带宽?

感谢lishiliang高质量的回复,很详细!公式推导应该都没问题,只是V3处的在环路中应该不是一个极点,而是一个零点。V3处的电容在高频下会削弱RS的负反馈作用,进而使环路增益增加,所以是环路中的一个零点。

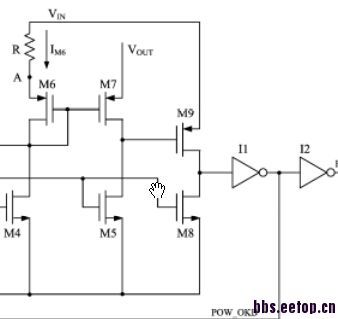

嗯,的确在实际上开关电源中SW点会有很大的ring,在系统设计中有两个方法减小SW的扰动引起的误触发。

1. 是SW不会直接接到V2点,而是通过一个RS低通滤波,从而削弱高频的扰动;

2. 系统中会有一定的blank时间,在开关动作后一定时间内,不检测电流采样电路触发的过流,所以即使有误触发,只要在blank时间内都没关系。

关于带宽的设计,取决于系统的要求,如果是开关频率上了MHz,Ts就是1us,可能最恶劣的Ton只有2,300ns,这样电流采样的时间估计只能是几十ns,这样你的闭环带宽就要求至少是10M以上。只要有了spec,其实就是电路设计过程,可以参见楼上的回复。

Mark。

终于看到有人问这个电路了,我有一点不懂,就是这个电路很多时候是作为比较器来用的,如果是V1端的变化引起输出翻转,这我可以理解,一个delta V引起的,但是如果是V2端的变化,引起输出翻转,我就不懂了,这个过程和V1有什么关系,感觉它自己这一侧引发的变化,求指教,我是不是太弱了。

补充一下,我说的这个电路和小编的稍有不同,就是负载是两个各自独立的电流源负载~

可以直接上图啊

建议上图,如果没错的话,你说的电路上面两个PMOS有一个是DIODE连接的吧。

是啊,就是你说的这个,我感觉diode连接的那个管子如果输入变化,是一个delta V,可是如果是另一个的管子输入变化,完全就是这一侧的影响啊,因为下面的两支路的电流源负载是两个独立的电流源,之间没关系啊。

我感觉小信号分析没意义。N3管应该是在截至去或者线性区都可以,电路本身是分流在Rs上的电流产生Vout输出,Gain是Rs/RD,很精确的值,N3什么区不重要。这个电路比较重要的极点应该在N1 Gate上和N3 Gate上,同时小loop产生零点。如果N1 gate极点小,V1和V2 同时降低或升高时,将在输出产生ripple, 在N3 gate上加Cap可以减小输出ripple。或者V1和V2上有Ripple,也可以通过在N3 gate上加Cap解决,更好的办法是在输出加filter。另外极点都可以做到高频,对电源电路影响应该不大。

通过N3的Cds产生的Ripple应该很小,主要通路是N3的gate到source。这是一个很不错的电路,他的精度只取决于P1和P2的Vth mismatch。

还有N1和N2的mismatch。哈哈,忘记看了

DIODE侧MOS管S端电压(V2?)变化,会引起Gate端相同的电压变化,因为bias电流是恒定的。这样不正是一个共源级(V1端不变)放大电路吗。

小信号分析得到开环loopgain还是很有必要的,因为GAIN=Rs/Rd的前提就是你的OP增益无穷大,如果N3的工作状态会引起环路增益很大的变化,这样系统offset会直接引起电路工作不正常。有条件建议搭一个试试,你会发现通常单级的这种结构都满足不了你系统的需求,最好是前一级是cascode结构。

你看上面这个 ,如果左侧源端变化,引起一个delta V变化,然后同时对右边造成影响,使输出翻转,可是右侧源端电压变化,引起输出翻转,这根本和左面没关系啊,这个delta V完全是自己这一侧决定的,和左边的输入无关啊,这还叫比较器么,大神指教,我是不是太弱了。

学习了

好吧,看来我之前讲的还是反的。你现在是VIN不变,VOUT变对吧,VIN不变,那左边电路就相当于提供一个Gate电压偏置,对吧? 那这个电路是不是就是一个共栅放大电路,Gate电压不变,S端电压变化,进而放大到D端电压变化,从而使输出翻转。这就是比较器啊。

是啊,可是这个过程只是一个共栅放大的过程,如何体现vout比vin高的时候,输出翻转,vout比vin低的时候输出又翻转的呢?也就是说这个放大器的工作怎么体现出来是VOUT和vin在比较呢,大神不要骂我,我想了很久,也许这很简单。

如何实现VIN和VOUT比较就看你静态工作点。理想的情况肯定是这样设计的,VIN=VOUT时,输出正好处于翻转的临界点,也就是增益非常大的工作点,也就是所有的管子工作在饱和区。如果下面两个bias电流一样的,那就是说要求上面两个管子W/L, VGS相等,W/L相等是你设计的,VGS相等就要求两个电阻上电压降相等,也就是电阻要相等。这样VIN=VOUT时,电路工作在一个增益很大的静态工作点,只要VOUT稍大于VIN,输出电压就会变化很大,输出就会是“0”或“1”。这不就实现了VOUT和VIN比较了吗?

不要想着VIN和VOUT比,只能是直接比,也可以是VIN-1V和VOUT-1V比较啊。

谢谢谢谢,我之前朦朦胧胧也是这么想的,总是感觉不确定,现在终于懂了,这自己想还是没有来个大神帮助给力啊~请问你是做哪个方向的?

嗯。

电路没啥问题,电阻串了是干什么的?