关于divider的noise与jitter的转换

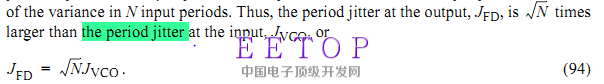

在 ken kundert 的“Predicting the Phase Noise and Jitter of PLL-Based Frequency Synthesizers”一文对PLL中各模块的noise和jitter进行了分析,其中对VOC输出的clock经过Divider的信号,divider的输入和输出时钟的jitter和noise有如下的关系:

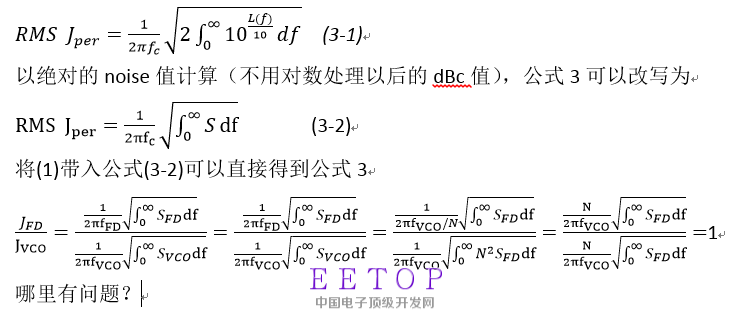

但是,根据jitter与phase noise的转换公式

不知道是哪里有问题!请高手指教

不好意思,附件里的图弄错了,忽略它

哪位大侠帮忙看看啊

静等高人指点

你这个里边Jper是period jitter还是phase jitter?要是period jitter公式好像有点问题吧

若是Phase jitter,确实分频后RMS jitter不变。

2分频后,jitter不变,T加倍,Phase Noise降低6dB.理想上,分频器应该对jitter没有影响。

对于白噪声产生的far offset frequency phase noise, /2-->phase noise下降3dB。

对于低频电压噪声产生 near offset frequency phase noise, /2--> phase noise下降6dB。

各位大侠,Jper是phase jitter

从电路分析,如果输入源没有jitter积累,synchronize divider之后的时钟,其jitter应该不变。如果divider的输入为VCO的输出,那么jitter应该有积累,但是从公式推导得到的结论不对,不知道是哪里出问题了。

根号N关系的公式说的是period jitter吧,后面推导用的公式是phase jitter