应用于PLL的可编程分频器divider

时间:10-02

整理:3721RD

点击:

大家好,设计一个PLL,其中需要一个可编程的分频器,2bit的,选择信号为00,01,10,11时,分频数分别为4,10,20,40。

那么这个分频器一般是怎么设计的呢?能不能用verilog代码写一个,然后综合成电路图,抄过来,但是综合后有的模块没有门级电路图。

或者有没有其他办法?

不需要频率综合里面的什么双模多模之类的这么复杂吧。

那么这个分频器一般是怎么设计的呢?能不能用verilog代码写一个,然后综合成电路图,抄过来,但是综合后有的模块没有门级电路图。

或者有没有其他办法?

不需要频率综合里面的什么双模多模之类的这么复杂吧。

分频数分别为4,10,20,40的话可以自己搭建组合逻辑的阿

4=2×2

10=2×5

20=2×2×5

40=2×2×2×5

做一个选通组合逻辑

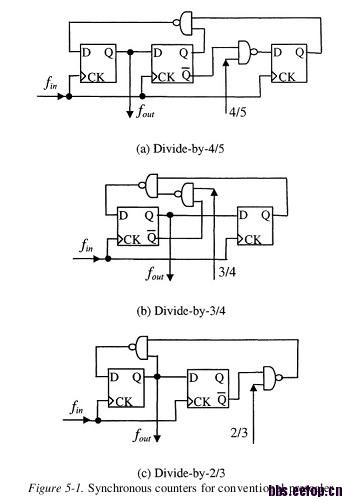

根据楼上的分析,关键是需要一个5分频器

看看这个电路

good

学习了

没有完全理解,能解释下图中的 4/5 3/4 2/3 分别都是什么样信号吗?谢谢。

你好,谢谢回复!

这个可编程分频器的最高输入要达到600MHz,可以用普通逻辑电路实现吗?还是得用到什么预分频之类的特殊电路呢?

要用高速逻辑分频的,200MHz以上

用TSPC,动态d flip flop

领教了

看你是什么工艺,130LG可能需要TSPC在2G以上,如果是90G,65LL,跑个3G分频不需要TSPC的。

是多模分频器,你说的是几个选通信号,为“0”是/2,/4,/4操作,为“1”是/3,/3,/5操作。

谢谢,可我画出来的波形图怎么不是简单的几分之一啊?