请教工艺角中的SF和FS

看过一个文章,说这两种情况是比较少见的,而且我们在仿真的时候也很少仿真这两个工艺角。

那么他们存在的意义是什么呢?求解。thx!

你看看process的测试图,tt是中心值,其他几个corner都是边界极限,都应该是在3sigma的位置概率应该是一样的。对于不同的指标,不同的结构,worst corner在任何地方都是可能的。

楼上,你理解的有问题。那是个参数分布图,不是概率分布图。

MOS管会出现F、S的情况,可能由两种情况导致,一种是栅的L出现细微的偏差,一种是栅氧厚度出现希望的偏差。对于栅氧,因为PMOS和NMOS的栅氧是一起长的,所以不管栅氧是不小心长厚了或者薄了,对管子的影响一样,所以一般只会产生FF、SS的情况。但对于L,如果N/P的栅方向一致,那么就很难出现N变长,P变短(SF)或者P变长,N变短(FS)的情况。但如果方向不一致,这就不一定了。甚至有些厂X轴和Y轴的工艺精度都不一样。

这也是为什么,在画版图的时候,通常要求栅朝向一致的原因。

1 你理解错了,我没说那个是概率分布图,因为横纵坐标都代表相同的量纲。我说在那张图上的边界处代表仿真model中几个极限工艺角,而其边界就是mc仿真中撒点的3sigma值,所以在边缘的可能性都是很低的。所以用工艺角仿真都是在仿mc的极限值,而且SF或者FS并不是真的S和F的组合,往往在中间的地方。

2 F还是S的出现不能光从尺寸上看,还有掺杂浓度栅氧厚度等工艺参数,np在不同阱所以差异肯定有,你看看model参数就知道F,S变化的是tox,VTH和迁移率等变化。我想因为tox应该是一起变所以vth相对变化不大,但迁移率一定是反着变的。而且WL的差异也不会说因为同向的原因而不变,不然大家就不用做mismatch了。

迁移率是反着变?另外载流子迁移率和浓度的关系是什么?

请复习半导体物理,谢谢。

另外,Corner是根据统计学计算出来的参数值。是为了覆盖最差情况,和真正生产中的良率不等价。

刚才那个没审核出来。重新回复你一遍。

关于迁移率是不是反着变以及和浓度的关系,建议你复习半导体物理。

FS和SF就是两个管子分别在F和S情况下的组合。不然你可以仿真看参数。3sigma不过是根据高斯分布计算出来的,和真正制造过程中的分布几率没有必然联系。

所谓反变是指相对tt来说S和F的变化相反,建议你好好看看model文件以及增加理解能力(我提高表达能力)

SF和FS绝不是一个S值和F值的组合,在我之前提到的图上就可以看出,那个图是椭圆的,如果是S值和F值的组合那么图应该是方形的。当然再次建议你看看model文件和工艺的datasheet。这个我们很多工程师都讨论过

最后,工艺制造过程同大部分自然现象一样遵循高斯分布,这个一般在mcmodel的sheet里面会有说明

抱歉,可能你接触的工艺比较高端,这方面比较严谨。我印象里看到的图是方的(但是刚才回去找没找到)。

刚才根据你说的去对比里下几个工艺,某大牌工艺做的比较好,各个管子在不同corner下的参数都有(tox,vth等);某小牌工艺就比较搓了,只有TT SS FF的参数,而FS和SF就是简单组合,所以变成方形。

可能这是就造成我理解偏差的原因。

另外,关于迁移率,N型载流子和P型载流子的变化是同趋势的。且在mos管的掺杂层面还不至于做到浓度影响迁移率的程度。

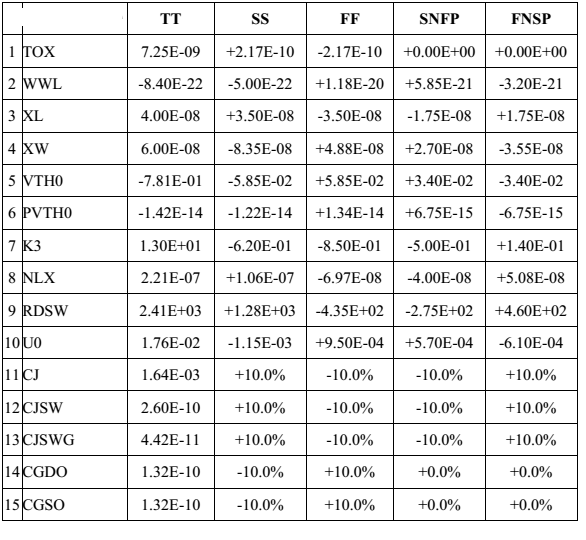

我这有张表,就是刚才说的某大牌工艺的,其中并没计量迁移率的变化,可以参考:

另外关于相对变化我再解释一下

假设n阱工艺,相对tt时候的掺杂,p掺杂增加了,n阱减小了,那么npmos的迁移率相对其tt怎么变化?可以理解了吧

掺杂影响的是浓度。浓度大的一定程度才会通过库伦散射明显影响迁移率。

掺杂的Corner会导致5%的迁移率变化?你这是哪家的工艺?

U的,不同工艺的迁移率都不一样,你觉得是靠什么控制的?如果按你的说法难道不同工艺的迁移率差别都是靠巨大的掺杂差别体现的?另外我觉得再差的工艺也不会把那张图画成方形的,你方便透露是哪家工艺吗或上图看看?

我想到一个问题,U0是建模的时候提取的参数,并不是半导体本身真正的物理特性参数。

迁移率主要受散射影响,这是基本的物理规律。施主受主杂质都主要以替位形势存在,只有当掺杂多到不得不形成大量间隙杂质的时候才会明显的影响迁移率。浓度对迁移率的影响很有限。

那个方形的图只是有印象,刚才没找着。没有给出FS和SF参数的是C家的。

表格是T家的,没有U0参数,我认为比较权威。

一些简单的model会做成方形的corner

严谨的会做成菱形,model的报告里一般都有corner的形状,

个人认为,影响器件特性的参数可以分成两类

1. 器件物理形貌,比如w,l,tox等

2. 材料特性,比如沟道浓度,介电常数,缺陷等

SF、FS器件在同一方向上的偏差受物理形貌影响较小

由于N/P管VT调整的注入是不同的工序,所以有可能造成VT出现SF,FS

说的那么复杂,不就是少子和多子的博弈吗。哪家的迁移率不是靠掺杂来控制的?你想想为何半导体要掺杂。

方形的别是示意图吧,你记错了。

涨知识了……

半导体掺杂是为了改变导电特性。重掺是为了提高电导率,通过降低迁移率来实现。

掺杂绝不是以改变迁移率为目的的。

空穴是价带顶电子运动的等效。所以电子动的快,空穴也比如动的快。

不要偷换概念,你之前说掺杂在一定数量级下对半导体特性影响不大,因此掺杂不会改变迁移率。那么如果一些基本电学参数都不改变那又何必掺杂,所以我问你为何要掺杂,你说改变导电性,ok,你答对了,那么导电性变了迁移率变不变?你这下不能说不变了吧,举例说如果说杂质替换1个单位和替换100个单位半导体导电性一样那么fab就不要去控制工艺了,随便做好了。

所以回到最开始说的问题但被你扯这么远的问题:因为NP管的掺杂失配导致的1)N管迁移率升高,P管迁移率降低2)P管迁移率升高,N管迁移率降低。你承不承认会发生?

顺便提示一下,迁移率是代表速度,那么S,F的英文缩写代表的意思是啥?

我说的是导电特性。还包括空穴导电还是用电子导电。而不仅仅是导电性。

影响半导体导电性,更有针对性的说,影响半导体电阻率的因素包括载流子浓度和载流子的迁移率。轻掺条件下,改变浓度是改变电阻率最直接有效的方式,而不需要改变迁移率。你举的例子也是改变载流子浓度,而不是改变迁移率。重掺条件下,会改变载流子的迁移率。但重掺不会用在mos管里。

“因为NP管的掺杂失配导致的1)N管迁移率升高,P管迁移率降低2)P管迁移率升高,N管迁移率降低。你承不承认会发生?”

这是不可能发生的,基本的物理规律你要懂。即使你给出的表,上面也只有一个U0,而不是U0n和U0p。

F、S的速度指的是管子开启的速度,不是载流子运动的速度。不然考虑C有什么用?

我想,恐怕你有必要去复习一下半导体物理和器件物理了。

顺便修正一下刚才的一个错误,重掺虽然会增加间隙杂质增加散射几率而导致迁移率下降,但却大大增加了载流子浓度,因此重掺一般是用来提高电导率的,把杂质半导体掺杂成简并态,主要用于形成欧姆接触。降低电导率一般是通过掺杂深能级杂质,提高载流子复合几率,在不增加载流子浓度的情况在降低载流子迁移率,从而实现高电阻率。

“轻掺条件下,改变浓度是改变电阻率最直接有效的方式,而不需要改变迁移率。你举的例子也是改变载流子浓度,而不是改变迁移率。重掺条件下,会改变载流子的迁移率。但重掺不会用在mos管里。”首先我们讨论的东西里面没有什么重掺杂轻掺杂,重轻只是相对来说,不要总用极端条件,另外这句话里面“而不需要改变迁移率”“而不是改变迁移率”“会改变载流子的迁移率”这些结论互相矛盾也和你之前说的掺杂不改变迁移率明显矛盾,建议你想好了理清思路再说。

(“因为NP管的掺杂失配导致的1)N管迁移率升高,P管迁移率降低2)P管迁移率升高,N管迁移率降低。你承不承认会发生?”

这是不可能发生的,基本的物理规律你要懂。即使你给出的表,上面也只有一个U0,而不是U0n和U0p。

F、S的速度指的是管子开启的速度,不是载流子运动的速度。不然考虑C有什么用?

我想,恐怕你有必要去复习一下半导体物理和器件物理了。) 始终不正面回答看来是自己也知道说错了。只有一个u0?你不会是以为NP的迁移率一样吗?真是不好意思我给出的表是Pmos的,以为你会懂,N的我懒得给你截图了,现在跟你说,N的表上也有一个U0,人家分两个表不代表没有Un,Up。恐怕你也不清楚这个U0在bsim模型中是怎么计算UN和UP的,建议你好好读读BSIM的模型。FS指的是开启速度?我还是给你多解释下吧:(摘)如果采用5-corner model会有TT,FF,SS,FS,SF 5个corners。如TT指NFET-Typical corner & PFET-Typical corner。其中, Typical指晶体管驱动电流是一个平均值,FAST指驱动电流是其最大值,而SLOW指驱动电流是其最小值(此电流为Ids电流)这是从测量角度解释,也有理解为载流子迁移率(Carrier mobility)的快慢. 载流子迁移率是指在载流子在单位电场作用下的平均漂移速度。至于造成迁移率快慢的因素还需要进一步查找资料。单一器件所测的结果是呈正态分布的,均值在TT,最小最大限制值为SS与FF。从星空图看NFET,PFET所测结果,这5种覆盖大约+-3 sigma即约99.73% 的范围。对于工艺偏差的情况有很多,比如掺杂浓度,制造时的温度控制,刻蚀程度等,所以造成同一个晶圆上不同区域的情况不同,以及不同晶圆之间不同情况的发生。这种随机性的发生,只有通过统计学的方法才能评估覆盖范围的合理性。

另外你考虑C只能说明你的逻辑比较混乱,我想你需要去学习一下半导体物理和器件物理了以及一些基本的逻辑推理知识。

还需要我把N的图贴上来吗?

什么是轻掺什么是重掺?相对概念?你要不要回去复习一下你的本科教科书?

““而不需要改变迁移率”“而不是改变迁移率”“会改变载流子的迁移率””

一段话这么多字你就看的见这三句?

1、“改变浓度就可以改变电阻率,所以不需要通过改变迁移率来改变电阻率。”这句话有问题么?

2、你举的例子,掺1和掺100,浓度上就有两个数量级的变化,电阻率是变大还是变小?迁移率是变大还是变小?对你所谓的“导电性”(非常不专业的一个词)的影响是浓度占主导还是迁移率占主导?

3、看不见我写的“重掺条件下”这几个字么?

到底是我的思路有问题还是你的阅读能力有问题?

载流子浓度,迁移率,电阻(电导)率,这三者之间的关系是什么?你最好回去理理清楚。

模型是干什么用的?模型代表物理原理?

按照你说的,T家的模型不考虑迁移率,所以T家工程师脑子进水了?

“1)N管迁移率升高,P管迁移率降低2)P管迁移率升高,N管迁移率降低。”

这种话都能说出来,和你解释你还强词夺理。考虑一下极端情况,电子的迁移率降到极低都走不动了,空穴还能跑的飞快?

再问个问题,掺的多了,迁移率是变大还是变小?你的F/S情况,对应的是掺多了还是掺少了?再看看你表格上迁移率的变化?

可能你的半导体物理已经忘完了。

真是贫嘴啊,啥叫抬杠,在这里就可以见识到了。说了半天,都是纸上谈兵,根本问题一点没解决。

1、“改变浓度就可以改变电阻率,所以不需要通过改变迁移率来改变电阻率。”这句话有问题么?有问题,所以和之前的句子没有因果性

2、你举的例子,掺1和掺100,浓度上就有两个数量级的变化,电阻率是变大还是变小?迁移率是变大还是变小?对你所谓的“导电性”(非常不专业的一个词)的影响是浓度占主导还是迁移率占主导?电导率就是表征其导电性的指标,怎么叫做不专业?给你掰开了写叫不专业,写的专业你又跟我搞混淆概念!你最好把话说清楚

3、看不见我写的“重掺条件下”这几个字么?服了,难道掺杂对其影响是非单调的?如果你认为是,你好好读书,如果你说不是,那么你说重掺杂条件下和轻掺杂条件下会造成相反的影响吗

到底是我的思路有问题还是你的阅读能力有问题?你的思路和阅读能力有问题

实在受不了你毫无逻辑的回帖,就简单就你这句话来说吧

" 这种话都能说出来,和你解释你还强词夺理。考虑一下极端情况,电子的迁移率降到极低都走不动了,空穴还能跑的飞快?"

我就问你,N管考虑的是p衬的掺杂,P管看的是Nwell的掺杂,考虑一下你说的极端但实际不会发生的情况,p衬重掺杂,nwell轻掺杂,那么会发生什么,电子迁移率是不是变低,空穴迁移率是不是变高?

混淆概念?你自己看不清楚,把我说的“导电特性”篡改为“导电性”。半导体物理里哪本书里用“导电性”这个词了?

轻掺条件下迁移率变化极小,可以忽略不计,重掺条件下会明显改变迁移率,我以为我在前面说过了你会看的进去,你是不是一定要纠结我省略了“明显”两个字?恭喜你,你已经成功的把原理辩论转移到语言和逻辑攻击上,你赢了。

既然你坚持强词夺理,那么我只好放弃解释了。

最后请你思考一个问题,浓度和迁移率的关系是正比还是反比?和Vth的关系是正比还是反比?你的表格中Vth和u0是正比还是反比?考虑考虑?呵呵。

千万别把模型当物理原理啊,亲!

脏字已编辑掉了。还请各位大侠别太责备小弟。

既然你出言不逊,还把污言秽语挂在嘴边,我想就只能不留情面直接打脸了

你说“混淆概念?你自己看不清楚,把我说的“导电特性”篡改为“导电性”,还jb胡扯。半导体物理里哪本书里用“导电性”这个词了?”

请去看《半导体物理学》(刘恩科著)第四章的标题,疼吗?好好读书好吗

鉴于你一被我指出错误就避而不谈我就简要打脸好了,我们争论的点就是你这句“迁移率是反着变?另外载流子迁移率和浓度的关系是什么?请复习半导体物理,谢谢。”“另外,关于迁移率,N型载流子和P型载流子的变化是同趋势的。且在mos管的掺杂层面还不至于做到浓度影响迁移率的程度。”现在我把之前懒得上的图给你上了如下所示,请你好好看看FNSP,SNFP中迁移率变化是不是相反的

我已经提醒你了Psub和nwell的掺杂相对tt的值可能是相反的会造成迁移率向相反方向变化,而你却不予理睬坚持自己的错误。还反复问我掺杂浓度和迁移率是正比还是反比。我严谨的回答你,既不是正比也不是反比,只能说掺杂越高,迁移率越低。我不明白你一直问我这种问题的原因和我们讨论的问题有任何关系吗,我反复跟你说这是相对增加或者减少,你却充耳不闻在错误的认识上越走越远,还动不动就让别人复习什么的,红字打脸。你说你是做工艺的,上过生产线吗?在那个fab?还是说在读书?哪个学校的?不介意说出来的吧?

A common practice to do SF and FS simulation as higher sensitive corners is the level shifter.

since the Nmos the driving cell and the Pmos is the latching cell, we need to make sure the nmos is strong enough to drive the pmos, so SF is usually the WST case.

“jb”是口头,改不掉,不代表态度,污染阁下视听了,不好意思。

多谢打脸,你不打脸我就不会重视,不重视就不会去翻书,翻了书发现刘恩科同志也不同意我说的,我表示自行掌嘴。不过貌似老刘在标题以后,再也没出现过这个词了么。为什么?我原来是想写“用'导电性'这个词来描述材料特性”,既然自己脑残删掉了,我认栽。

亲,我说的反比是广义上的反比,不是反比函数的反比,别那么字字珠玑好么?既然你说了掺杂越多 迁移率 越低。那么请问,掺杂越多,Vth是变高还是变低呢?现在表上迁移率变高的同时Vth减小,请问是掺杂多了还是掺杂少了?你U0对浓度敏感基本上要到掺10^18cm^-3以上,沟道里是多少?都没好好考虑过我问的问题,就来有意义没意义的,亲,不动脑子就开口是最没意义的,就像我口出秽语一样,一点意义都没有。

亲,别把模型当物理原理了,我就知道你会把两张表贴上来给我看,就是典型的把现象当原因,把儿子当爹,做工程的脱离理论久了都容易犯这个错误。模型是为了拟合曲线而进行的数学处理,虽然基于一定的物理原理,但还是会为了拟合而校正参数。U0变不变,建模型的人可以根据具体的情况的考虑,目的不过是为了让模型拟合的更准确。我贴的表上根本没有把U0当变量,你又怎么解释?难道T家的人都是废物?

通过调节杂质浓度来改变沟道内载流子迁移率是徒劳的,在沟道里,1个量级的浓度变化引起了多少迁移率的变化?老刘书上有写,烦请自行查阅。

至于动不动就查户口的,我就懒得奉陪了。我是哪的之前在论坛里说过,您老确实有心,自己翻吧。

胡搅蛮缠也要有个度,这次你说的甚至有些不知所云了,净举一些正确的说法,然后没有因果的得出你错误的结论。下面再打几次脸,望你想好再说话

公司里的不好弄,弄上来也涉及版权,就用网上公开的资料吧

这个是某大学课程链接http://www.ee.columbia.edu/~kinget/EE6314_F05/project_anu/ee6314/F05/TSMC018_teaching.scs

大学名字不用我说了,可以看到。这个是他提供的t018的工艺文件

摘抄其中几段:

* 6/ process variations are modeled by varying:

* - CJ and CJSWchanges junction caps

* - TOXchanges cox

* - VT0 changes on currents

* - U0changes on currents注意看,你在12L说“施主受主杂质都主要以替位形势存在,只有当掺杂多到不得不形成大量间隙杂质的时候才会明显的影响迁移率。浓度对迁移率的影响很有限。”你在23L说“ 轻掺条件下迁移率变化极小,可以忽略不计,重掺条件下会明显改变迁移率”我知道你是看了课本知道的,但你没有实际接触过工艺控制,所以不知道实际的工艺掺杂在什么地方,另外这个变化率极小到底是什么量级,现在这里告诉你,实际掺杂的浓度会对U0造成影响,究竟多少,我贴的U的有,这个T的下面也有。

下面是各个工艺角的参数,我们那ss和ff来看,看到u0n/p了吧,ff是在tt基础上加,ss是在tt基础上减,幅度是多少?可以看到是+-10%哦,现在你还说“浓度对迁移率的影响很有限”吗,现在告诉你不光T,哪个fab都要关注掺杂对u0的变化,因为u0是spicemodel的基本参数。你说“ 通过调节杂质浓度来改变沟道内载流子迁移率是徒劳的,在沟道里,1个量级的浓度变化引起了多少迁移率的变化?老刘书上有写,烦请自行查阅。” 别总让别人查书好吗,先自己读读书读读资料查查网络,现在你告诉我,迁移率+-10%的变化工艺厂是怎么搞出来的哦。

library tsmclib

section tt

parameters pctvariation = 0

parameters toxn = 4.1E-9

parameters toxp = 4.1E-9

parameters cjn = 9.840057E-4

parameters cjp = 1.165397E-3

parameters cjswn = 2.405513E-10

parameters cjswp = 2.042242E-10

parameters u0n = 262.117234

parameters u0p = 112.30168

parameters vth0n = 0.362587

parameters vth0p = -0.3881948

include "TSMC018_teaching.scs" section=mos

endsection tt

section ff

parameters pctvariation = 5

parameters toxn = 4.1E-9*(1 - pctvariation/100)

parameters toxp = 4.1E-9*(1 - pctvariation/100)

parameters cjn = 9.840057E-4*(1 - pctvariation/100)

parameters cjp = 1.165397E-3*(1 - pctvariation/100)

parameters cjswn = 2.405513E-10*(1 - pctvariation/100)

parameters cjswp = 2.042242E-10*(1 - pctvariation/100)

parameters u0n = 262.117234*(1 + 2*pctvariation/100)

parameters u0p = 112.30168*(1 + 2*pctvariation/100)

parameters vth0n = 0.362587-0.1

parameters vth0p = -0.3881948+0.1

include "TSMC018_teaching.scs" section=mos

endsection ff

section ss

parameters pctvariation = 5

parameters toxn = 4.1E-9*(1 + pctvariation/100)

parameters toxp = 4.1E-9*(1 + pctvariation/100)

parameters cjn = 9.840057E-4*(1 + pctvariation/100)

parameters cjp = 1.165397E-3*(1 + pctvariation/100)

parameters cjswn = 2.405513E-10*(1 + pctvariation/100)

parameters cjswp = 2.042242E-10*(1 + pctvariation/100)

parameters u0n = 262.117234*(1 - 2*pctvariation/100)

parameters u0p = 112.30168*(1 - 2*pctvariation/100)

parameters vth0n = 0.362587+0.1

parameters vth0p = -0.3881948-0.1

include "TSMC018_teaching.scs" section=mos

endsection ss

最后贴一下黄昆的半导体物理第一章节选,打你在23L和26L说的“ 混淆概念?你自己看不清楚,把我说的“导电特性”篡改为“导电性”,还jb胡扯。半导体物理里哪本书里用“导电性”这个词了?”“多谢打脸,你不打脸我就不会重视,不重视就不会去翻书,翻了书发现刘恩科同志也不同意我说的,我表示自行掌嘴。不过貌似老刘在标题以后,再也没出现过这个词了么。为什么?”

我给你补充个,还有施密特等类似利用到P,Nmos 阈值特性的模块或者电路。

还是用模型解释物理,完全扭不过来。我能说什么呢?“孺子不可教也”?不对,应该是你的人格过度成熟导致无法接受对已形成一定时期的认知的改变,甚至会对这种改变抱有敌意。

亲,你怎么不试试先告诉我掺杂浓度变化了多少?能引起了多少迁移率的变化?

模型中TT的数据是测量后统计平均的。请问Corner是怎么来的?你应该不会认为直接从晶圆测量出来的吧?我想你测过晶圆上的工艺分布情况吧?麻烦你描述一下是什么形状好么?同一个cassette里的分布一样么?

我贴的T没有U0,这个T的是.35的,你的贴的T家的有,是.18的。你有没有看到我说的 “U0变不变,建模型的人可以根据具体的情况的考虑,目的不过是为了让模型拟合的更准确。”?又选择性失明?迁移率的±10%是不可控量,在10^15的浓度下,高出差不多一个量级的浓度变化才能改变1个单位的迁移率,这就是我说的“影响有限”,难道这些fab的浓度不可控性要达到±50%?你还敢让fab干活?

“但你没有实际接触过工艺控制,所以不知道实际的工艺掺杂在什么地方,”哈哈,你知道掺杂在什么地方?求求你告诉我好吗?要不让我猜猜,MOS管的模型里的迁移率一定是从Poly2上提取出来的,一定是的。

好吧这个笑话太冷了。我还是拜托请你想想沟道是什么情况,你想在沟道做重掺杂?做电容是挺合适的。

影响迁移率的只有杂质浓度么,亲?我不是让你回去复习半导体物理了么?晶格你知道的吧?应力你知道的吧?缺陷你知道的吧?能想明白为什么0.18工艺考虑了u0,0.35没考虑么?这是因为尺寸缩小让沟道内的平均迁移率对局域晶格常数更敏感。晶圆本身就不是均匀的,亲;SiO2虽然是非晶但是对Si依然是有应力的,亲;离子注入还是比较容易形成缺陷的,亲;这些才是工艺的不可控性啊。Corner是为了考虑工艺不可控性而存在的,你怎么就知道个掺杂啊,亲?呵呵,这个问题我和你提了两三遍了,我本来想通过展示Vth和U0的关系引导你自己想到这个问题的答案,你居然说我的问题毫无意义,唉。你要我说什么好

最后,关于“导电性”,我已经自行掌嘴了。不过,你干嘛不把我说的“我原来是想写“用'导电性'这个词来描述材料特性”,既然自己脑残删掉了,我认栽。”这句话一起贴出来?避重就轻?混淆视听?还是看漏了?

我说刘恩科老人家在后文中没有再用“导电性”这个词,你扯黄老的书是嘛意思?穿越了?就算你扯黄老的书,黄老也是在开头用的这个词来引入进一步的概念,在后文中出现了么?为啥他俩都用在开头?这个问题我问过你,可你压根没当回事吧。这些是教材啊,亲,是给半导体入门的人用的基础教材啊亲。“导电性”是个普适概念,只能用来笼统的描述“好”和“坏”,放在开头可以给非专业的人士引入专业的概念,这是叫专业词汇?再说你见过有谁说“某某材料的导电性是xxxx(鬼也不知道的单位)”这样的话?你这样说话么?

亲,我一直在和你解释的u0这么大变化不是浓度掺杂引起的。请回顾下你在争辩什么?你把模型贴上来说u0会变,也罢,所以就推出u0变化是由且仅由浓度引起?你自己看看你说的对么?请问你是在打我脸么,亲?我怎么只听到半空中啪啪的响,现在已经是冬天了,你不是在打蚊子吧?

平心而论,虽然你不太听进的别人的话,但总体上你还不错。

Anyway, 我这都是在胡搅蛮缠,你大可不必理会我

确实,迟滞区间对阈值很敏感。SS和FF通常只是造成区间平移,但SF和FS则会改变区间大小。