关于瞬态仿真过冲过大

时间:10-02

整理:3721RD

点击:

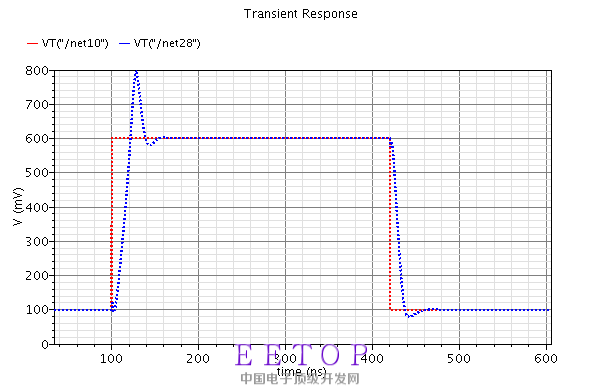

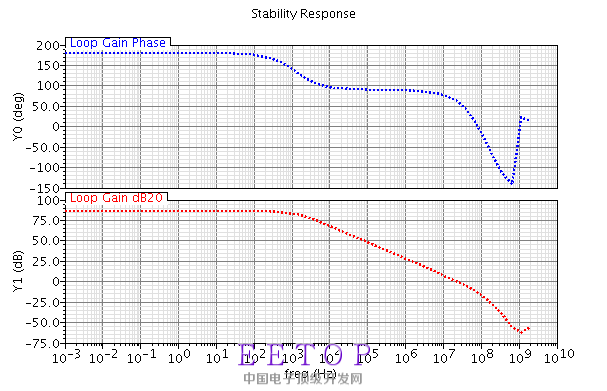

我在完成DC,AC仿真后进行瞬态tran仿真,但发现过冲过大。但是进行AC仿真时的相位裕度有54度,增益为80dB.为什么呢?

此电路主要用于buffer

我是新手,求指教!

相位曲线尾巴又翘起来是否有影响?

此电路主要用于buffer

我是新手,求指教!

加强BandWidth或者SlewRate,这两者是一致的。

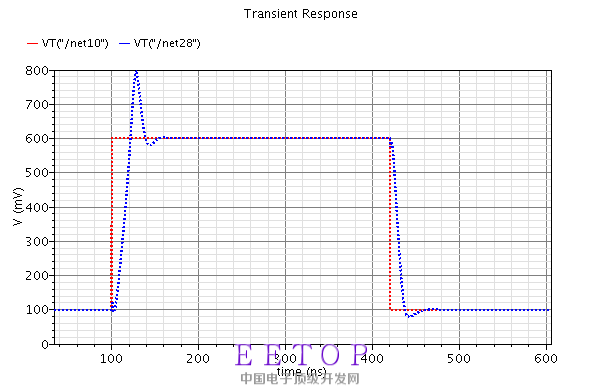

谢谢!我采用的是最简单的二级放大结构。我在输出级增大电流后过冲明显减小,但是在通过增加输入管的W/L来增大gm值,增大GBW的方式并不理想。

此外,采用增大输出级电流后,有一个如下图的现象,不知道是否影响。

相位曲线尾巴又翘起来是否有影响?

应该不影响

谢谢!还发现一个问题,采样的电压和实际输入的电压大概会有0.2mV以内的固定偏差,对于这个问题有什么方法可以减小吗?因为要保证10/12bit的设计进度。

再补充问一下,相位图尾巴上翘的主要原因是什么呢? 我知道更极零点有关,但还不会分析。

开关的馈通效应和运放的增益带宽共同影响offset,可以减小但很难完全消除。相位上翘应该是多个高频零点凑一块去了。