全差分运放的verilog-A

`include "discipline.h"

`include "constants.h"

module diff_opamp(vout_p,vout_n,vref,vin_p,vin_n,vsupply_p,vsupply_n);

input vref,vsupply_p,vsupply_n;

inout vout_p,vout_n,vin_p,vin_n;

parameter real freq_unitygain=1e6;

parameter real gain=835e3;

parameter rin=1e6;

parameter real ibias=0;

parameter real rout=80;

parameter realiin_max=100e-6;

parameter realslew_rate=0.5e6;

parameter vin_offset=0;

parameter real vsoft=0;

realgm_nom;

realvmax_in;

realvin_al,c1,r1;

electrical vout_p,vout_n,vref,vin_p,vin_n,vsupply_n,vsupply_p;

electrical cout_n,cout_p;

analog begin

@(initial_step or initial_step("dc"))begin

c1=iin_max/(slew_rate);

gm_nom=2*3.14*freq_unitygain*c1;

r1=gain/gm_nom;

vmax_in=iin_max/gm_nom;

end

vin_al=V(vin_p,vin_n)/2+vin_offset;

//

//input stage

//

I(vref,vin_n)<+ibias;

I(vref,vin_p)<+ibias;

I(vin_p,vin_n)<+(V(vin_p,vin_n)+vin_offset)/rin;

//

//GM stage with slew rating

//

I(cout_n,vref)<+ V(cout_n,vref)/100e6;

I(cout_p,vref)<+ V(cout_p,vref)/100e6;

if(vin_al>vmax_in)begin

I(vref,cout_p)<+ iin_max;

I(vref,cout_n)<+ -iin_max;

end

else if(vin_al<-vmax_in)begin

I(vref,cout_p)<+ -iin_max;

I(vref,cout_n)<+iin_max;

end

else begin

I(vref,cout_p)<+0.5*gm_nom*vin_al;

I(vref,cout_n)<+ -0.5*gm_nom*vin_al;

end

//

//dominate pole

//

I(vref,cout_n)<+ c1*ddt(V(vref,cout_n));

I(vref,cout_p)<+ c1*ddt(V(vref,cout_p));

I(vref,cout_n)<+ V(vref,cout_n)/r1;

I(vref,cout_p)<+ V(vref,cout_p)/r1;

//

//output stage

//

I(vref,vout_n)<+ V(cout_n,vref)/rout;

I(vout_n,vref)<+ V(vout_n,vref)/rout;

I(vref,vout_p)<+ V(cout_p,vref)/rout;

I(vout_p,vref)<+ V(vout_p,vref)/rout;

//

//soft output limiting

//

if(V(vout_p)>(V(vsupply_p)-vsoft))

I(cout_p,vref)<+gm_nom*(V(vout_p,vsupply_p)+vsoft);

else if(V(vout_p)<(V(vsupply_n)+vsoft))

I(cout_p,vref)<+gm_nom*(V(vout_p,vsupply_n)-vsoft);

if(V(vout_n)>(V(vsupply_p)-vsoft))

I(cout_n,vref)<+gm_nom*(V(vout_n,vsupply_p)+vsoft);

else if(V(vout_n)<(V(vsupply_n)+vsoft))

I(cout_n,vref)<+gm_nom*(V(vout_n,vsupply_n)-vsoft);

end

endmodule

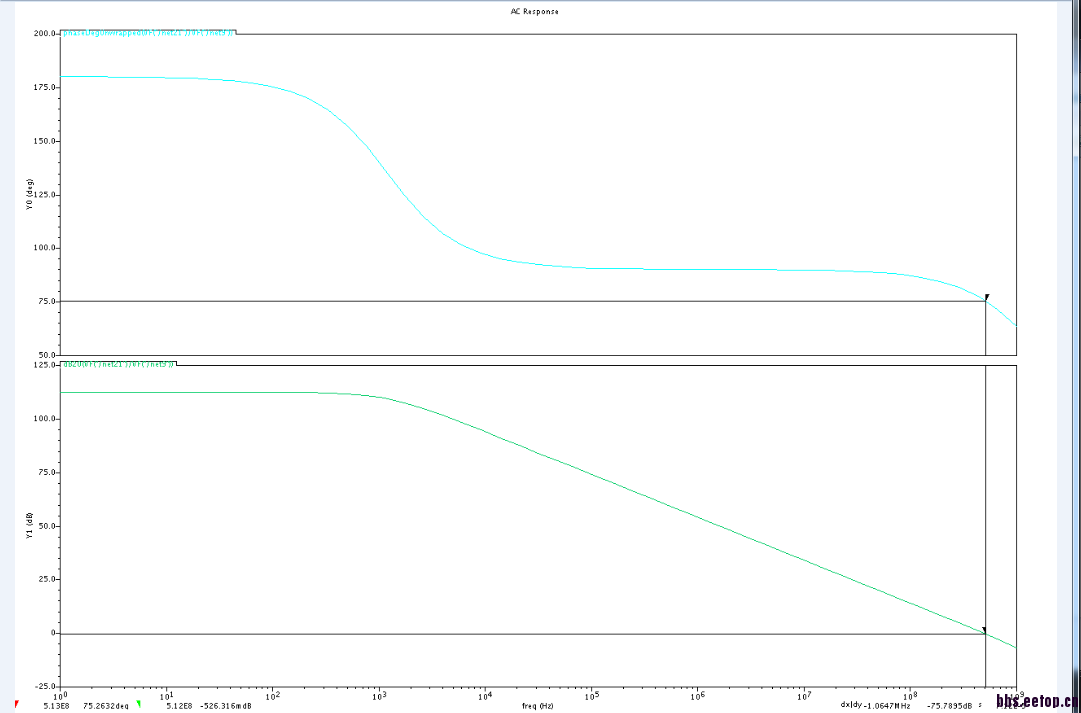

增益和相位曲线

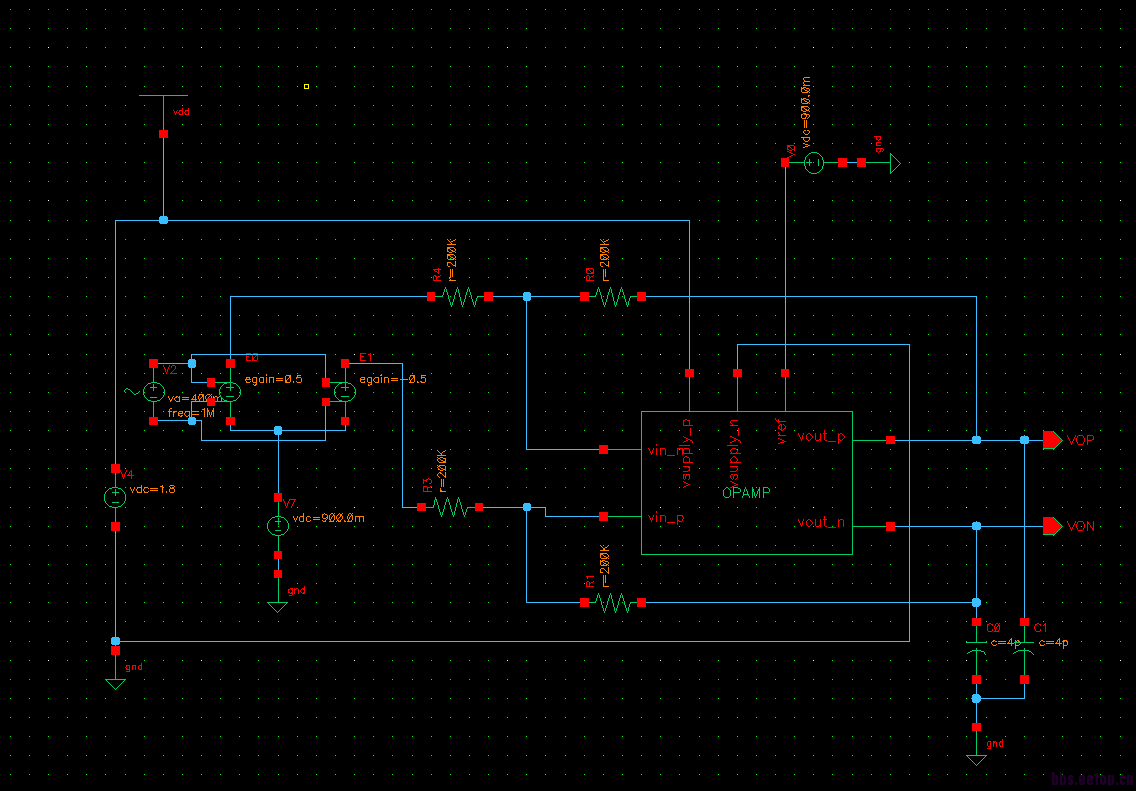

仿真的电路图

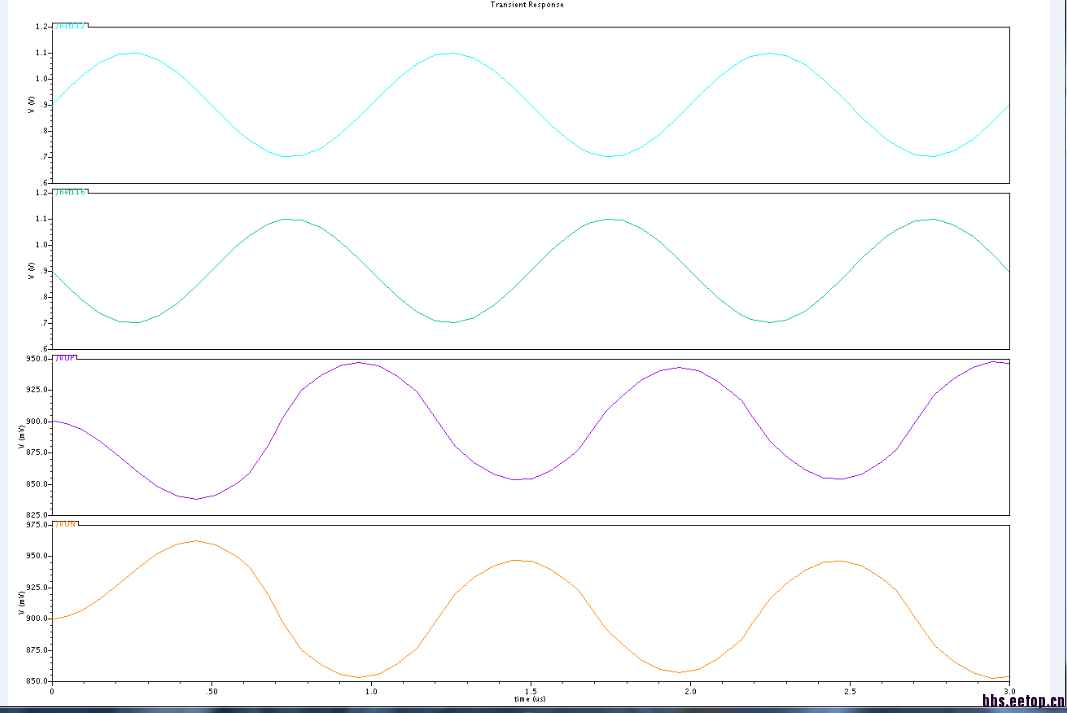

我接成增益为1的情况。正选波输入,为什么输出的波形是这个样子的,下面两个是输出

有人知道吗,就简答啊

瞬态有个建立过程很正常,主要看稳定后的

看圖好像 OUTPUT 和INPUT 間有相位差嗎?

freq1M => 100Khz ,

parameter real freq_unitygain=1e6;=> 100e6

你在 sim..

如果

freq1M => 100Khz ,

parameter real freq_unitygain=1e6=>

還是有差異 但比先前 input signal 1Mhz 好很多了

不只是相位,峰值也有问题,输入峰值200mW,输出峰值才50mW,而且输出看起来也不想是sin波,圆圆的。您的意思是我的仿真输入信号频率高了吗,改成100KHz?

hspice sim

input signal 你先降低看看 ..

.hdl 'full_diff.v'

.OPTIONS BRIEF=0

.param d_vcc =5

x1vout_p vout_n vref vin_p vin_n dvdd 0diff_opamp

vcc1 dvdd 0 pwl(0,0 1.5u,0 2.2u,d_vcc)

vss2 gnd 0 0

vss1 dvss 0 0

v1p0 vipn0 sin(0,0.4,100k)

vinvinn0 sin(0,0.4,100k,0.5m)

vn0 n0 0 0.9

vref vref 0 0.9

r11 vip vin_p200k

r12vin_p vout_n 200k

r21 vin vin_n200k

r22 vin_n vout_p 200k

c11 vout_p 0 4p

c21 vout_n 0 4p

=======

module diff_opamp(vout_p,vout_n,vref,vin_p,vin_n,vsupply_p,vsupply_n);

input vref,vsupply_p,vsupply_n;

inout vout_p,vout_n,vin_p,vin_n;

parameter real freq_unitygain=100e6;

parameter real gain=835e3;

parameter rin=1e6;

parameter real ibias=0;

parameter real rout=80;

parameter realiin_max=100e-6;

parameter realslew_rate=0.5e6;

parameter vin_offset=0;

parameter real vsoft=0;

=>real freq_unitygain=100e6;

thanks very much

确实是输入频率降低,波形就正常了,谢谢啦。

real freq_unitygain=100e6;这个意思是单位增益带宽是100MHZ吗,但是具体测出来却不是这样的,我把这个1e9,带宽却达不到1GHz

我输入100KHz的信号,输出还有有个延迟,700ns多,幅值上也有点衰减,只有在输入50KHz的时候输出才和输入一样,但是这个输入信号频率这么低,我又不能用,我应该改那里才能使输入频率高的情况下没有这个延迟,并且不衰减啊,可不可以指点一下

全差分的,实际带宽只有1半

好东西下来看看!

学习中!

运放里的soft output limiting valye是什么意思?

感谢小编分享

那个是模型是错的

请问这个模型哪里错了呢?谢谢~

LZ,这个模型怎么可以提高响应频率?

谢谢~

我尝试改了模型中的slew-rate后效果比较明显,freq_unitygain也是关键。