求助,求助!关于ahdllib中opamp的那段代码

时间:10-02

整理:3721RD

点击:

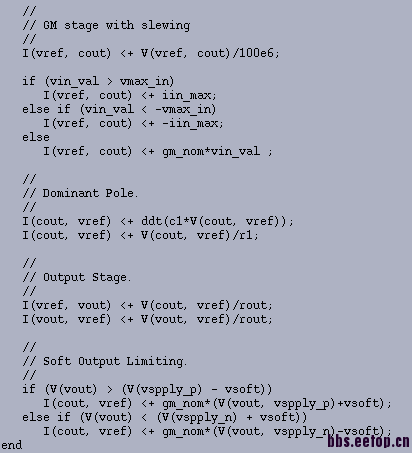

ahdllib中opamp的veriloga代码中,cout是个什么东西?怎么看都看不明白。v(vref,cout),I(vref,cout)到底指的什么?cout 只是定义了一个 electrical,到底是个什么东西?输出电容吗?如果是的话怎么和vref联系起来呢?多谢,多谢! 备注:vref 为1/2*vdd,

ahdllib中opamp的veriloga代码中,cout是个什么东西?怎么看都看不明白。v(vref,cout),I(vref,cout)到底指的什么?cout 只是定义了一个 electrical,到底是个什么东西?输出电容吗?如果是的话怎么和vref联系起来呢?多谢,多谢! 备注:vref 为1/2*vdd,

[img][/img]

你需要画出这段代码的小信号电路图才能完全明白,cout是中间middle gain stage的输出电容的节点电压,vref在ac等效时是虚拟地,在dc时是控制输出共模电平的电压,你再好好画画模型的电路图吧。

多谢,多谢!我是初学veriloga.能把该运放的小信号图给我画一下吗?这是一级运放吧?但是你看那个输出级的代码怎么感觉像是二级运放?如果是二级运放那个电容是米勒形式的吗?

在output stage中又一次出现了cout,这个与你所说的“Middle gain stage” 怎么联系起来?

goodgood

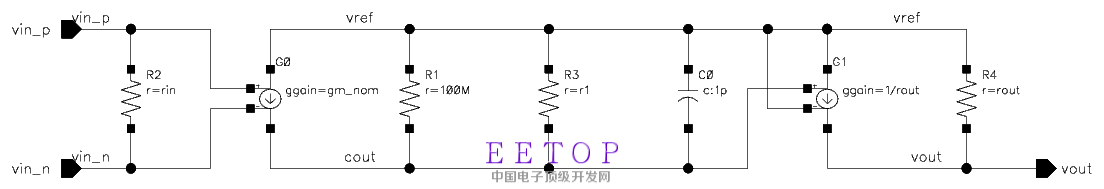

电路的小信号模型如下:

其中cout基本上就是输出信号,只不过为了不使负载干扰gain和bandwidth,后面又加了一级0dB gain的buffer. buffer的输出叫vout。

另外,model中关于soft-limiting的部分没有画出来。