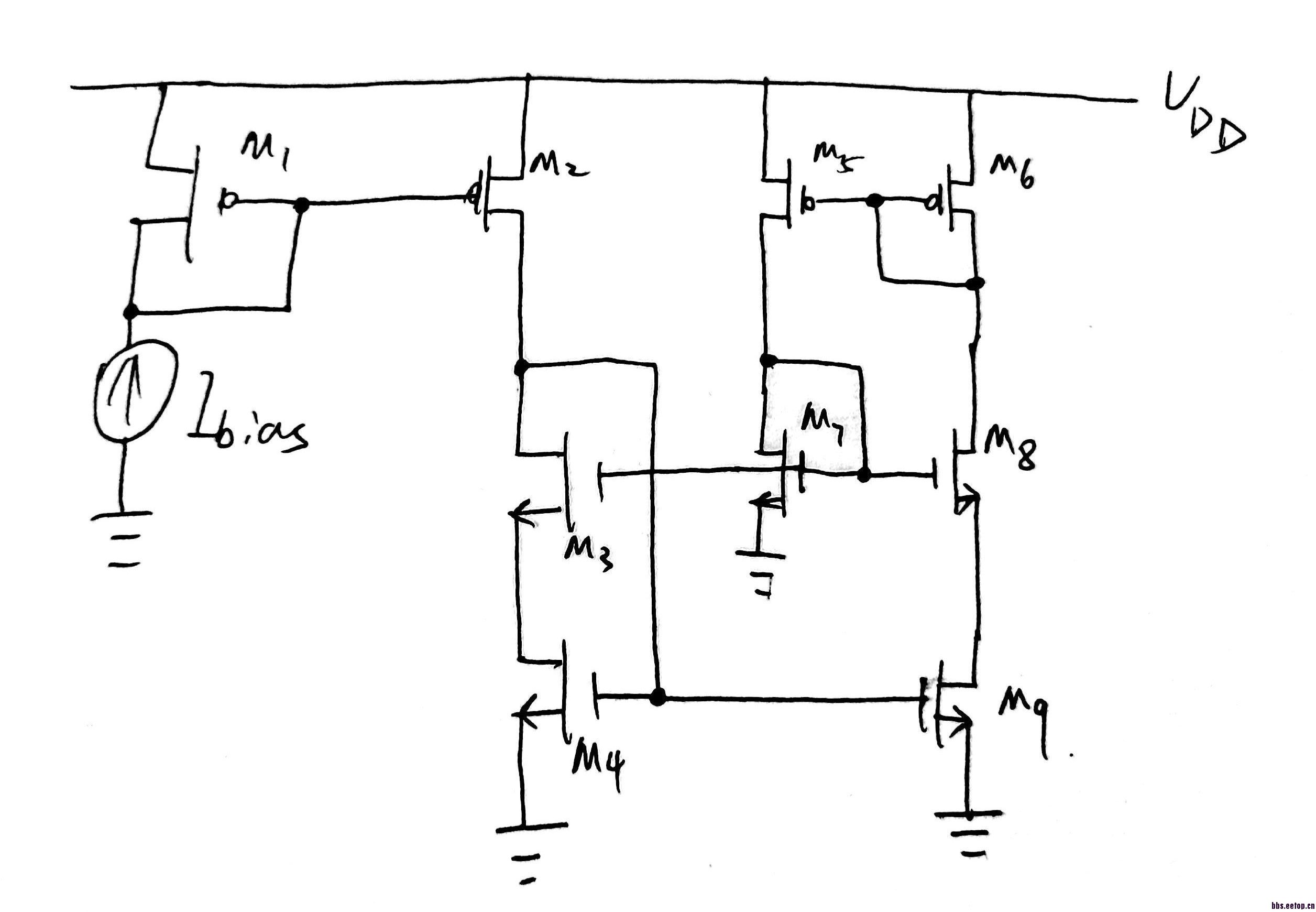

面试中被问到的一个问题

面试官说这个电路中所有管子都可以工作在饱和区,然后问这个电路有没有问题?

本渣见识太少,当时也不知道从何入手,面试官又提示说从自偏置电路可能存在简并点的角度考虑一下,但我觉得好像右边有个0电流简并点就没有其他了吧?

左边的低压cascode是什么意思?需要考虑吗?

屌炸天的Ibias

你确定M1,M6,M7画对了?

见笑了我重新改了一下图

改了

cascode的偏置有问题,也就是简并点啦。

右边的0电流简并点也没什么不对,延伸一下,把cascode也带进去。

拉扎维书中有讲,与电源无关的偏置章节。面试官根据应用稍微改了点形式。其实这种结构没有启动问题,拉扎维认为有问题,大家都跟着认为有问题。

电路中没有画出EN(PD)的管子,若该结构EN=0时,M5和M7的gate分别为VDD,VSS(即都关掉),之后EN变成1,若不加启动电路,M5和M7gate 怎么开启?

漏电可以开启。如果要快速开启,可以加启动电路。

我是想说不启动的兼并点是不稳定点。

那仿真就能验证了,但没见到开启过。都需要启动电路

不稳定的兼并点,不是还有可能启不来么,加了启动电路肯定不会有问题,但不加不好说,

如果M7的栅压保持0,那么M3就关的死死的,

M2把M1 的电流镜像过来会对M4的栅电容进行充电,直到把M4的删拉到VDD才罢休,M4栅压很高了,它是想工作的,无奈只能工作在线性区。

这个时候M3就很关键,它的漏端电压为VDD,栅端电压为0,它如果很淡定,那电路就不工作了,它要是漏端和栅端之间有漏电(小尺寸工艺),就会给M3的栅电容充电,然后把栅压抬上去,电路就工作了。

仿真不一定准,我们分析过。或者device一点漏电都没有。我们也还是加的,只是要搞清楚为什么加。

我仿真的都是能开启的哎

只要有不启动的可能性,还是要加启动电路。

那你是加不加启动电路呢?就给你这个原理图,没说工艺。

那你仿真漏电有多大?

小工艺下M5 的ds漏电应该比M3的dg漏电大很多吧,起来也是M5漏电启动的。

nA级别

M3的dg漏电和M5的ds漏电那个大?

你那个是16nm工艺?

把M8 short掉,就没有启动问题了

说的有理,小尺寸工艺指的是多小的工艺?

起来需要多长时间呢?

这个必须同意

短掉电路不就被改了吗不清楚这个电路是干什么的当时这是最后一个问题了时间比较急我也忘记问面试官这种电路作用是什么

实际电路中这是用来干什么的?

M6 M7需要启动电路

28nm,IO 管

电流镜,或者与电源无关的偏置