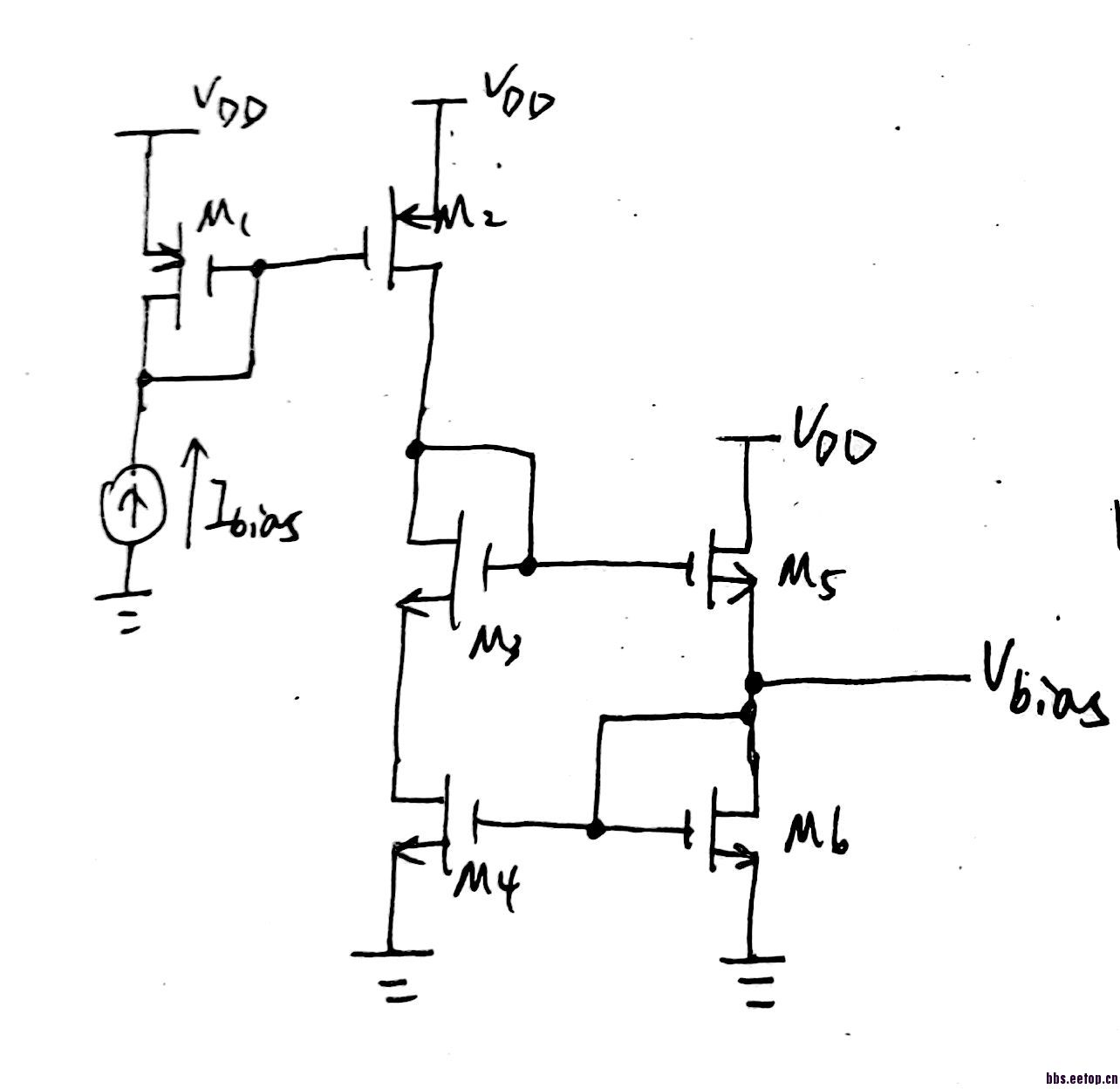

这种偏置电路是提供电压偏置的?

遇到这样的偏置电路,M6漏端给出偏置Vbias ,M2应该是线性区吧,这个偏置是给follower的,有没有人能讲一讲这个偏置有什么好处,常用吗?之前看论坛上讨论过电压偏置和电流偏置的优缺点的这种电路是不是就是一种电压偏置电路?

电流镜。不过最后的电压偏执从M6的gate 输出浪费,还不如不要M5,M6。直接用M4做diode的gate输出。因为该电路没有省如电压 headroom,浪费一路电流

我刚看到的时候也觉得好像相对普通的电流镜并没有什么优势我以为可能是稳定性或者什么方面更好在我看到的电路中很多地方都用这种结构,Ibias是从电流源模块拉过来的之后经过这样的电路给其他电路提供偏置比如follower以及放大器

M2应该是线性区?这有什么好处?看不出来

起到电阻的作用使电路脱离简并点确定两支路电流

补充一点,这个要看用途的。如果说有点好处的话,就是输出节点看到vdd的阻抗较小,多了几百毫伏的电源 headroom,如果是一般的应用,可有可无。

同意二楼

1. M2是电流源,不能在线性区;

2. 输出是Class AB,适合驱动大的电容负载或者负载端可能有抖动耦合的情况.直观来讲,原来的diode形式的电流镜输出阻抗只有1/Gm,而且输出端负方向的slewing rate受限于M2的电流;现在输出阻抗是2/Gm,并且双方向的slewing rate都由Gm来决定。

如果VDD为典型3.6V的话。

M2漏端电压2Vgs,这个可以一定程度上减小M1和M2由于沟道长度调制效应引起的电流匹配误差。

后面两路类似cascode镜像,所以电流镜像匹配较好。

所有管子都应该工作在饱和区。

个人观点,欢迎指正。

M4下面少个电阻吗?

不少 我以为M2应该起电阻的作用

电压偏置么?能否仿真下看看Vbias会不会随VDD变化?

是电压偏置给follower的电流源栅极提供一个电压看起来会浪费电流我确实要仿一下会测一下PSR不过这是超牛公司的电路总觉得人家这么做是有道理的只是自己还没搞清楚

如果这是超牛的公司的产品,那么他这么做的道理很可能就是故意让你看不懂。

小编这么说还是有道理的这要是真的简直细思极恐这种偏置还不是一个地方这样,有些放大器的的尾电流偏置也是这样还有些电路的设计感觉超过了小弟的认知范围,比如follower的电流源L并不是很大,输出阻抗看起来比较小,使得小信号增益比1小了很多,可是做缓冲器的电路减小了输入信号并不有利于后级电路处理······

对于某些公司的产品,如果没有能力进行工艺层面的剖析,还是放弃吧。

这个是用于ADC 输入级驱动的input buffer?可能是要做一个环让vbias 的稳定吧?

他们肯定是看高大上芯片,那些工程师没这么无聊

毕竟还是有些公司会用改变工艺参数的方式,对常规工艺里做出来性能很差的电路进行改进,从而达到让别的人无法复制的目的。

前辈猜的对确实是一个input buffer 但目前的情况确实是像我前面跟帖里面说的 电流源L比较小大概是最小沟道长度的两倍多点通常来讲这并不符合希望的接近1的增益但还有个问题是由于模拟通路的带宽比较宽,考虑到摆率的要求应该有大电流偏置,这样对电流源尺寸的要求又会比较大(非常大),如果让W/L同时增大几倍,那么follower的尺寸简直是不可接受的。至于这个偏置电路做成这个样子,我想应该是在Vbias或者PSR方面相比普通电流镜偏置好些吧

哦?小编知道有公司这个干?

TI是自有foundry就不说了,其他的大一点的会有驻厂PE。

小编应该是抄高速ADC 的线路,这种产品一般不搞这个,怕弄巧成拙

你说说看这个input buffer 驱动什么样的电路?多少bit 多少MHz 的adc, 这样比较容易,几V供电。

哦哦,前辈说的是。

超高速adc防抄主流在后端数字校正里做手脚了吧?

有的时候是整体工艺参数会优化,比如说pmos ,nmos 阈值调调,或者电阻电容值调调之类的。必须要保证一致性。

了解,多谢前辈指点。

驱动采样保持电路具体多少位分辨率 速度多快 我就不透露了就像你后面讲的即使他们要调参数也是整体优化应该有这种可能实在不行这就得自己来了

呵呵,你这样的不够厚道。需要人帮忙还不提供足够的信息。那您就慢慢弄吧。

扯得都够远的,这不是书上的基础电路呢