偏置电路中电容的作用

右下角的C6大约4ff=4e-15f,它起什么作用?有的说是补偿用的。我见过另外一个电路和这个结构完全一样,而没有用电容C6!

仿真的时候发现,加上这个电容,bias电压有一个大波动(峰峰值有几十u),而没有电容很小(几个u的峰峰值)

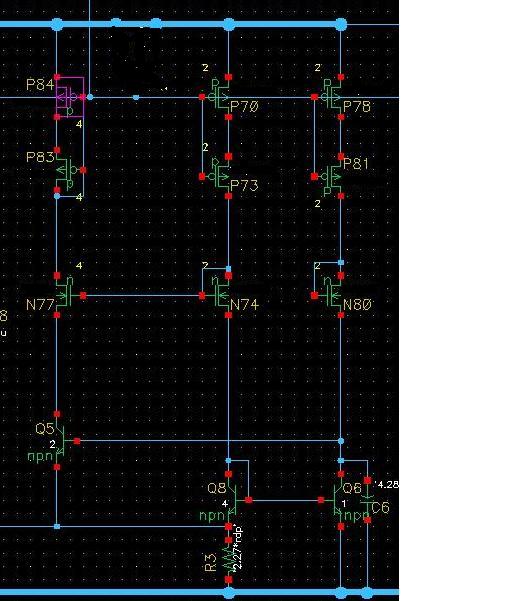

bias电路

仿真了一下

tran分析时,有这个电容,在bias电压上叠加一个峰峰值几十uV的波形,没有这个电容,峰峰值降低位几个uV,就是加上电容,bias稳定性变差了!

tran分析时,vdd突变,无论有C6,bias都很稳定。

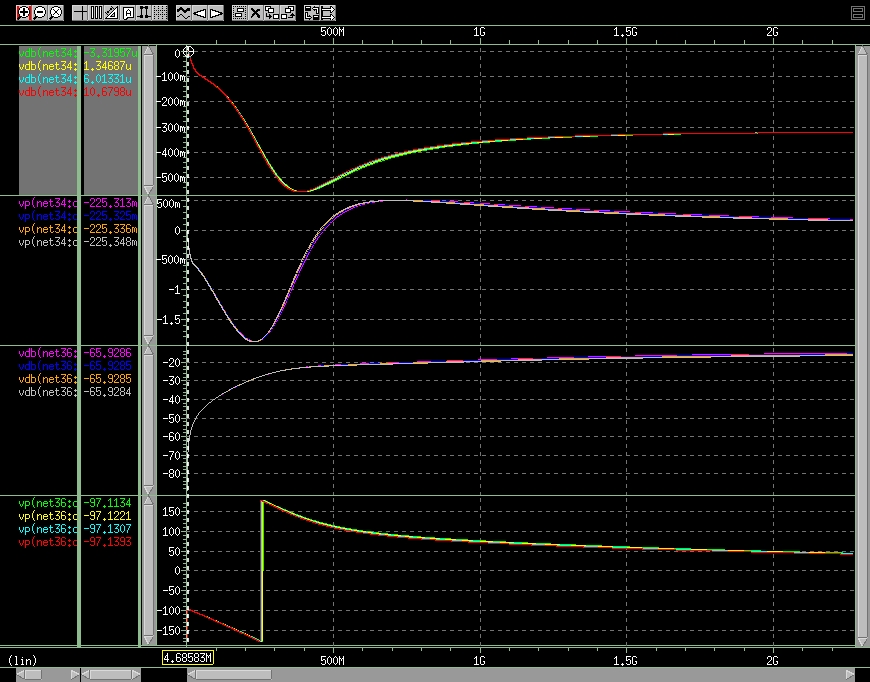

ac分析,在vdd上加ac信号,发现无论是否有C6,bias和其他电压均无明显变化,且在Q5基极的增益很小,小于-20db,而且随着频率升高而增大,但有限;

断开Q5基极,在此加ac信号,发现有无C6,结果变化也很小。

電容一般是要加的(把pole拉近原點)

這是self-compensate結構

畫出bode diagram就會看出差異了

我一般會用ac 做sweep C值

找出最穩定的值後再run tran

山外青山樓外樓

西湖歌舞幾時休

暖風薰得遊人歸

直把杭州作汴州

謝謝

谢谢楼上!

可是我是得到的波特图啊(见下图),是在vdd加ac信号吗? 下图是在vdd加ac信号(加上对电容的sweep),net34是bias的波形,net36是Q5基极的波特图,其增益都很小啊,怎么会出现稳定性问题,还需要补偿? 图中有对C6进行sweep,可是不同的C没什么变化啊?

可否解释清楚一点?

bias

我也很想知道,这个电容的具体作用,究竟是怎样来补偿的,为什么要加,这里的补偿是启动哪个作用,看起来不想米勒电容,对地的电容,不是会增加极点吗?

感觉不是补偿而是用于启动 和电荷泄露的

Sometimes a small cap parallel can restore the phase margin.Did you check the phase margin?

我也觉得是稳定性的考虑,可以仿真一下有没有电容时的phase margin

另外我觉得这个电容从连接上应不是启动用,因为在上电时,npn并不会导通。

LZ做AC时不应在VDD加ACsignal,而应在电容节点加

C6 looks like a parasitic cap coz it is only 4fF range. Is it possible for worst case simulation purpose? In real circuit, usually I don't think you have "true Cap=4fF"

To be continued, and that is why w/o C6, your bias ripple is so small, while w/i C6, ripple gets bigger.