veriloga中数组size不匹配,来看下咋回事,谢谢

时间:10-02

整理:3721RD

点击:

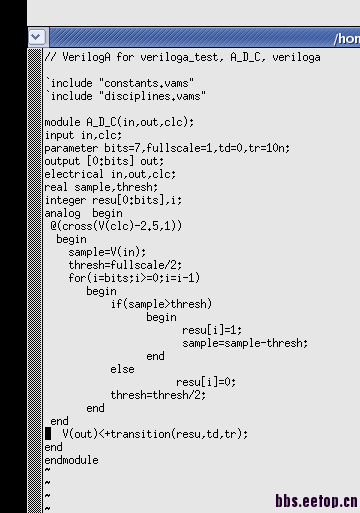

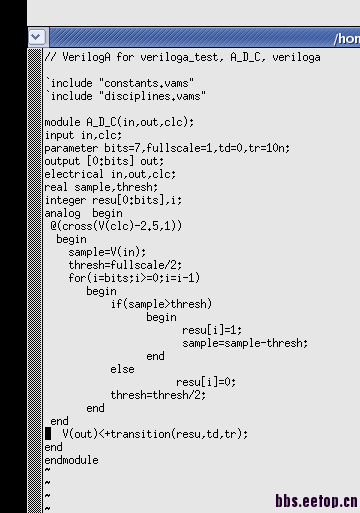

刚同样的这个问题发错地方了,重新发一下,求指导

坐等大神解释下啊

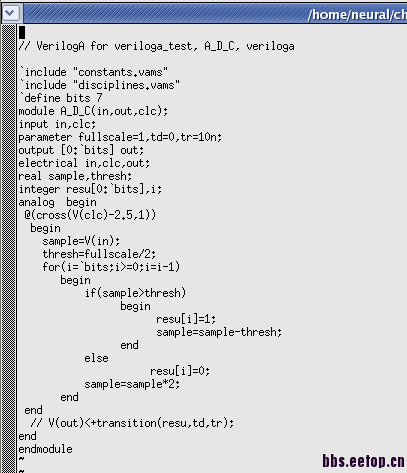

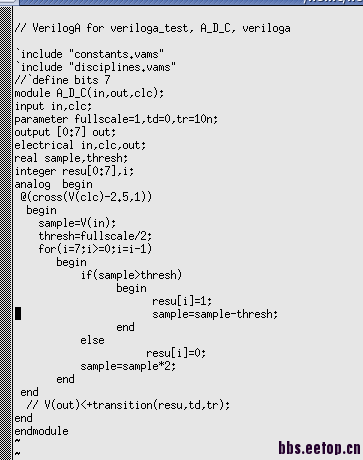

可能是out pin定义时在range中“[0:bits]”使用了参数bits,好像veriloga不能在pin的range中使用参数,你可以试试先把range中的bits换成一个常数试试,如果想要使用可变化的range,好像可以用“`define BITS 4”这样的语句

手册上的一个例子

`define BITS 4

module adc (in, out) ;

input in ;

output [0:`BITS - 1] out ;

输出output时,应该写成循环才行吧?把resu 依次输出到 V(out)里。

我把那个赋值语句都改成注释了,也不对啊

electrical out可能需要带上range才行,手册上的一个例子

electrical [1:10] node1 ; // Declares a vector net

如果还是找不到错,建议一句一句注释掉查找问题。比如,先注释掉整个analog模块,只留下端口和参数定义的语句试试。

搭车请教一下,有没有VerilogA 方面的书推荐两本啊,先谢啦

没,就是从论坛上下的东西看看