CSD97376Q4M三态测试及DSP 的EPWM配合使用问题

TI的工程师,您们好!我有两个问题请教,希望能尽快得到你们的指点!

问题1:

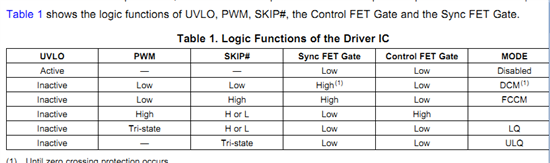

CSD97376Q4M的PWM端口支持三态输入,逻辑功能表如下:

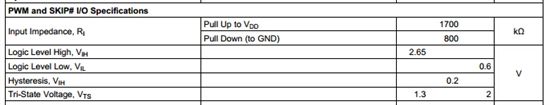

测试时,csd97376的供电为5V,半桥FET两端加的电压为6V,SKIP#端口上拉为5V,PWM控制信号有函数发生器提供。pwm为5V信号时,控制管和同步管可以正常的开通。当我想关断两个管子时,我给的PWM信号高电平为2V,低电平为1.4V,此时控制管的管压降为1.5V,同步管的管压降为4.5V。然而,继续切换至正常的5V pwm信号,两个管子的压降没有变化。掉电重启后,再给5V pwm信号,两个管子正常开通与关断。请问是什么原因?

假如 两管正常的开通与关断定义为状态1,两管均封锁定义为状态2。我的目的是利用PWM端口或者SKIP#端口 在状态1与状态2之间自由切换。请问如何做到?

问题2:

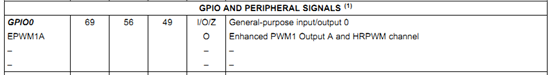

假如能解决问题1,即我的目的是利用PWM端口或者SKIP#端口 在状态1与状态2之间自由切换。当我采用TI的dsp型号为TMS320C2803X时,如何达到在状态1与状态2自由切换的目的。CSD97376Q4M的驱动PWM来自epwm模块,如下:

PWM功能时只有输出特性;该特性下,应该只能有高电平、低电平的脉冲方式输出吧,是否能呈现高阻特性?

图挂了

图已经补上

楼主,手册里面已经讲得很清楚了,PWM引脚的高电平是最低要达到2.65V,低电平不能高过0.6V。不明白你自己定义的高电平2V和低电平1.4V是想做什么,另外你讲的这个时候两管的压降,是在说VDS?照你样的电压来看,其实此时上管和下管都处于微导通的状态。你试一下给PWM一个恒定的在1.3V到2V之间的电压,不要再给一个电平变化的PWM信号,再去看一下两管的VDS电压。

对于你说的,两管封锁,是想驱动的输出处于高阻态?你的电路应用对效率要求特别高么?需要在某些时候驱动芯片直接三态?如果这样,你可以使用一个具备三态的IO去控制skip#引脚,这样就可以实现状态的切换了,而且skip#处于三态时,整个驱动芯片的损耗最低。

感谢你的回复!现在问题已经解决。

根据手册,给一个处在0.6v-2.65v之间的任意波形的电压都应该是关断的。实测低压为1v,高压为2.1V。

我的电路对效率要求高,会采用skip#端口做控制。

罗工:

你好。

你的回复中提到”如果这样,你可以使用一个具备三态的IO去控制skip#引脚“。这种实现方式没有问题。

现在TI 栅极驱动器的PWM输入端均具有三态特性。那么如果脉冲由DSP的PWM接口提供,请问DSP软件 是怎么做的?我现在是必须用直接用DSP的PWM口封锁脉冲。选择芯片为UCD7232.

wilbert:

你好!

我现在也遇到了同样的问题!csd这款芯片,用SKIP#做控制引脚。

我初步的想法是,I/O口产生PWM高电平信号,再外部分压,给一个1.5v固定电平给SKIP#脚,禁止两路MOS开通。

你是怎么解决系统运行过程中随时停止芯片内部两个MOS管输出的?