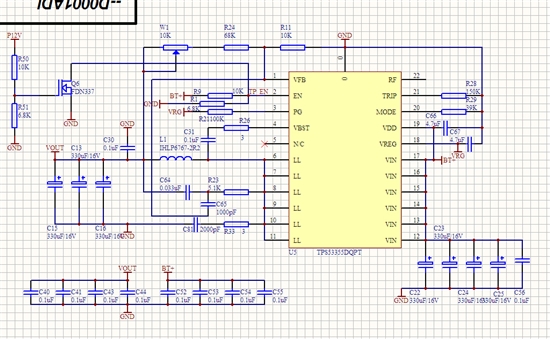

TPS53355DQBP ripple injection circuit的参数问题

大神 能帮我算一下 ripple injection circuit的参数么 我输出电容现在是4个 330uF/16V的固态电容, Vin最小值5.5V 典型值 7.4V 最大值8.4V Vout 5V 15A 频率500Khz 电感2.2uH - IHLP6767GZER2R2M-01 输出电容 固态电容330uF/16V 4个 C1电容 33nF R7 5.1K R1 10K 现在是输出电流到8A以上就震荡,表现在设备上就是设备自动关机 开始我觉得是过流保护了 Rtrip 选的值是150K 算出的保护电流10A ,但是根据“4544.TPS53355 Design Spreadsheet”文档,Rtrip最大值是200

电路

PCB

你可以进到tps53355的主页

http://www.ti.com/product/TPS53355?keyMatch=tps53355&tisearch=Search-EN

使用右侧的webench 设计纹波注入参数。

考虑到你的输出为5V,15A,则输出功率达75W,这样高的功率,如果效率为90%,那么损耗高达8W以上,芯片损耗一半也有4W,所以需要考虑良好的散热。

我试过了 好玩我现在的电路区别不大 就是电感两端并联的电阻电容值有点区别,然后输出电容是4个100uF,我用4个100uF试了下 还是不行 还震荡,但是我电容是以前在市场随便抓的 ESR可能比较大 官网给的是TDK的 ESR 2.3毫欧 ,在就是电感,我用的电感是2.2uH的 DCR是2.41毫欧 ,工具给出的是0.82uH DCR0.5毫欧 ,但是DCR大小应该只影响效率,不会造成不稳定。可能是我现在输出电容ESR较大,或者输出电容距离芯片太远 造成回路太大 所以不稳 还是什么别的原因呢

干扰到纹波注入电路,使注入的纹波偏离三角波,都会使片子的开关频率抖动较厉害。

所以控制回路和功率回路一定要良好的分开,然后在电容的地方合到一起。

电容的ESR不会造成太大的影响,影响较大的是环路的寄生电感,特别是输入环路的寄生电感,所以输入电容一定要是低ESR,ESL的,尽可能的靠近芯片的电容。

输入电容与芯片要as close as possible。

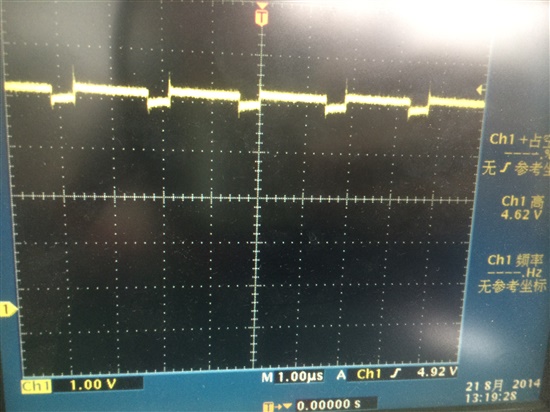

纹波注入电路指的是VFB环路嚒 ,我注意力一直集中在输出,真从来没对输入做过调整,新买的TDK电容也是按输出买的 明天我调下输入电容位置试一下 现在 VFB到是3角波。就是上面又振铃的那种干扰,而且PGOOD引脚叠加了一个幅值不是很大的方波,这页应该是不正常的吧

1.VFB上的振铃可能是由于示波器探头导致的,请将示波器探头的地线去掉,然后使用一根短导线作为地线与示波器探头做连接。

2.PGOOD上的方波频率如何,与开关频率相同的话,说明你的输入阻抗有点高,输出高频回路面积没有控制好。

我对输入电容的位置做了调整,变化是有的,但是不是很大,电流只增加了1A,

PGOOD的方波频率的确是和switching是一样的 ,您不说我以前还没注意这一点。

角度没照好 抱歉

高频回路面积PCB已经固定的情况下 有什么解决办法么

还有一个问题,当电流升到一定值之后,开关频率就稳不住了,系统调节变得不是改变占空比,而是改变频率了,我现在设置的是500k,最高的时候频率能到620k,switching的幅值也明显下降约400mV

输入输出压差太小,会进入调频模式。

压降说明你输入路径的阻抗太高,请使用更粗的导线和更厚更宽的铜皮。

输入环路太大,那就飞线吧,直接将电容接到芯片的引脚上,不过这仅限于实验。

还有一个问题;TPS53355这个芯片有自保护功能么?因为我现在是电池供电,每次电池充完电之后(8.2-8.4V),输出电压都是0,但是我测了芯片VIN、VDD都是正常的,这个时候我给芯片重新上电一下,就可以正常工作了。(充电时我会将EN引脚拉低,使这个芯片不工作)

我找到问题的原因了

之前测试了一个多星期都没问题,但是上周开始又出问题了,震荡再次出现,并且工作一段时间,EN引脚电平自动拉低了,正常的时候EN引脚时分压过去的。电压应该是5.8V,但是工作一段时间之后,EN引脚电平莫名其妙的变成4点几V,Vreg正常,PG低电平,没有输出,有的时候EN 直接就0.6了,然后可能在重新焊接一下,又好了,可以工作一几十分钟,然后就又不行了,然后在重新焊一下 ,可能又好了,就这么循环往复。。。

楼主,你之前的问题解决了,可以跟大家分享一下,原因是在哪里。至于你说的EN引脚电压,你可以先试一下,单独从外部给EN一个固定电压,看看电路工作是否正常。你的电路图上,EN引脚还受另外一个MOSFET控制,另外一个MOSFET的门极电压是从P12V分压么?如果是12V,那么一旦有12V电压,Q6开通,EN会被拉低的,EN拉低了,低到0.6V时,芯片就不能正常工作了。

之前的问题就是因为,干扰比较大,功率级电路和控制信号没做好隔离,后来改成四层板了,将功率级和信号中间用了一层地做了屏蔽。

然后说现在的问题,现在我控制EN引脚的MOS管是没有焊的,所有不用考虑P12V过来的控制信号。现在现象是开始的时候芯片可以正常工作,EN引脚从输入电源分压得到到5V电平。但是工作一段时间之后,EN引脚电平突然拉低了,可能拉低到4.几V,也可能0.6V。但是无论拉低到多少,只要低于正常的分压值了就没有输出,PG也是低,但是VREG是正常的。以前干扰比较大的时候,是EN 是正常的 不会被拉低,电流加上去,系统震荡,然后重新启动,就可以了。现在是EN被拉低了 就一直是低,系统无法在工作了。但是我对板子进行下重新焊接,就又能用了 ,但是用一会还是出现这个想象,就这么循环着,有的时候我改变EN引脚的分压比例,系统也能在此工作,但是也就2S 就又不行了。

很没头绪。

我现在手里的电路板状态是这样的 :输入电源8V,正常工作时:输出5V 空载;EN引脚4V;VREG引脚5.08V。故障之后:输入电源8V;输出0V;EN引脚1.2V(可变-低于4V,变化频率不是很高。)VREG 引脚6.87V-7.55V。

故障之后:重新上电:状态不变-故障状态

断电静置(2min以上):输出5V 空载;EN引脚4V;VREG引脚5.08V。但是该状态只能位置2-4s。在断电,在静置,循环上述过程

重新焊接:输出5V 空载;EN引脚4V;VREG引脚5.08V。可维持时间不确定,但肯定大于1min。

楼主,用示波器测试一下你的VREG波形,同时观察一下SW引脚电压和EN电压。看看到底EN引脚电压的跌落是哪里引起的。最好把测试波形上传一下。另外,你的新layout可以参考一下TPS53355的规格书里面的布局。

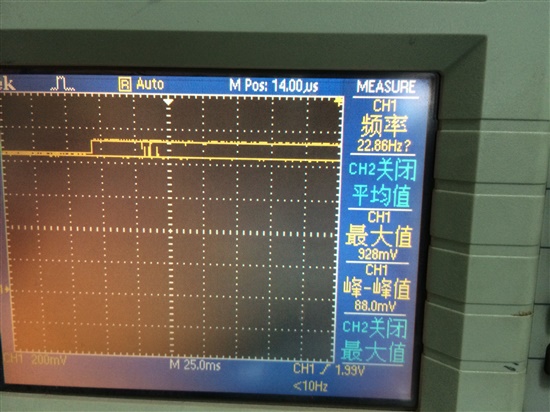

故障之后:VREG=(5.18-7.2);波形:

EN引脚波形:

SW=0V;

正常工作状态的波形没有捕捉,因为现在这个板子 正常工作的时间实在是不长。

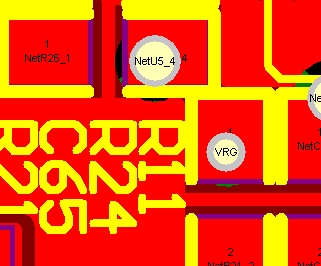

目前PCB结构,功率层:

信号层:

VREG接100K上拉和VBST(NetU_4):

1. 请详细描述这个状况发生的前因后果。是空载上电后过一会儿发生的?

2. 芯片是否过热?

3. 板子不工作 后是否可以修复?

1、上午做过实验了,空载-带载都会出现这个现象:上电一段时间,EN引脚莫名拉低的情况,区别是:空载-SW波形有震荡,带载-载荷越高-波形越稳定。此电路PCB一共投产12块,最初做出2块,无论空载还是,满载,波形都稳定。

其中一块PCB装在样机中使用了一个多星期,突然出现EN莫名拉低的情况。具体情况:因为电路设计是充电时,禁止放电-采用的方式是,充电电源端有电压则控制MOS管将TPS53355EN引脚拉低。但是后来充电电路中,有电压倒灌到充电电源端,造成即使不充电状态,EN也被拉低,这个问题引起的原因应该是充电电源端没有泄放回路,只要将电池断开在连接就可以,但是每次都需要重开开关比较麻烦,所以将控制EN电平的MOS管去掉,希望系统变成可边冲边边放的。之后 EN 引脚自动拉低的情况就开始出现了。然后重新焊接了 N 块板子 也都出现了这个问题。

另一台是只使用一个循环就出现该现象(锂电池充满电,在用TPS53355电路放电,此为一个循环)。

2、芯片无发热现象

3、断开电源,放置几分钟,芯片可以再次工作,但是工作时间比较,从目前的情况看,静置时间越久,再次工作维持的时间越长。(至少我昨天下午实验时,静置几分钟的话,芯片再次空载工作只能维持几秒钟,但是今天早上重新上电之后,带载使用约1分钟。

4、重新焊接也可再次工作一段时间。

您好,

TPS53355单独工作是否正常,就是说,撇开系统级的东西,TPS533355电源子模块是否正常?

考虑到这很有可能是系统级的问题,如果方便,可以上传系统级的电路图,也可以发到我的邮箱 Jason-shen@ti.com ,帮你检查一下。