关于LDO Ripple rejection的一点疑问

时间:10-02

整理:3721RD

点击:

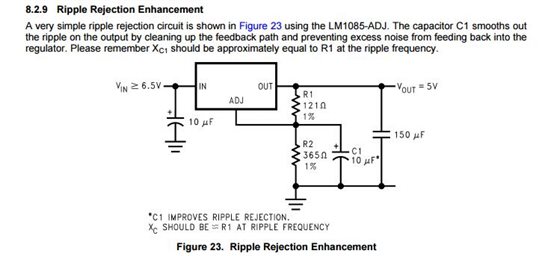

看数据手册的时候

看到Xc should be euqal to R1 at ripple frequency。我想知道,如果我LDO输入的噪声是500K的,那么我这边f设置成500k附近呐还是说设置的越低越好。因为

看到Xc should be euqal to R1 at ripple frequency。我想知道,如果我LDO输入的噪声是500K的,那么我这边f设置成500k附近呐还是说设置的越低越好。因为

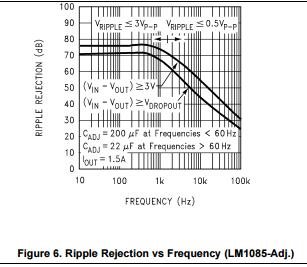

看到频率低的时候纹波抑制比很高。这里希望TI的工程师帮忙解释下,如果我LDO输入端噪声500K,那我设置成500K附近还是越低越好。

看到频率低的时候纹波抑制比很高。这里希望TI的工程师帮忙解释下,如果我LDO输入端噪声500K,那我设置成500K附近还是越低越好。

LM1085在500kHz时的PSRR很低,如果你对这个性能很在意,不太推荐用这个产品。

Cadj可以选10uF或22uF,然后再确定R1。

或者可以选择TPS7A4501。

Hi

LM1085对于高频率下的ripple rejection效果不好。

或者你可以在前段在增加一级LC.

ldo的压差可以允许有多少伏。纹波电压可以小到多少。

lDO允许大约3~5v

Hi

压差一般由功耗决定,也就是说最大功耗时,只要芯片温度不会超过其限制,是可以允许较大压差的,只不过压差越大,意味着很可能效率越低。