TPS56121EVM power down 测试时重启的问题!

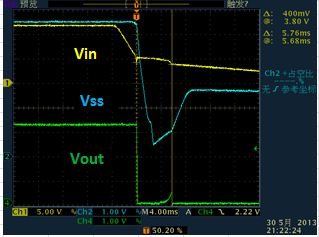

见测试波形:power down时,会发生Vo重新启动的问题,用什么最好的方法解决此类现象?

Hi

从第一个波形看,在powerdown时,Vss的电压没有被拉掉,所以实际上你需要检查是什么控制着你的SS/EN脚的电压,需要将这个脚彻底的拉低到0.27V一下。

或可以参考datasheet: http://www.ti.com.cn/cn/lit/ds/symlink/tps56121.pdf 第一页用一个MOS来控制。

你的测试条件是什么?在EN脚挂一下分压电阻是否可以解决?

Hi,Johnsin!非常感谢你的回答!Powerdown时,EN/SS引脚拉至0.27V一下,是个非常好的方法!但还得需要一个MOS管,同时需要一个MOS管的驱动信号,相对成本高且设计复杂! 该问题是由于Vin掉电后,低于UVLO后,又有个反冲的电压大于了UVLO,导致芯片重启问题!除了加大EN/SS引脚的软启动电容值,还有什么更好的方法?谢谢!

Hi, Kevin. 测试条件:断掉Vin=12V,观察Vo=3.3V的变化!结果后面出现重启的现象!

• the EN/SS pin voltage must be greater than VIH

• the input voltage must exceed UVLO on voltage VUVLO

The UVLO has a minimum of 500 mV hysteresis built-in. 我觉该从以上方面着手解决!

Hi

你所指的反冲电压来自于输入源吗? 还是其他,有有没有办法从这方面控制,因为从你的波形上看输入的电压在powerdown时并没有直接降下去。

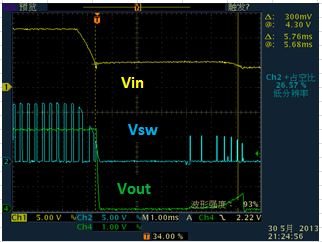

就是把EN欠压,看看关断的情形

Chris Cui

Hi, Kevin. 测试条件:断掉Vin=12V,观察Vo=3.3V的变化!结果后面出现重启的现象!

• the EN/SS pin voltage must be greater than VIH

• the input voltage must exceed UVLO on voltage VUVLO

The UVLO has a minimum of 500 mV hysteresis built-in. 我觉该从以上方面着手解决!

Hi,

Johnsin, 我指的就是输入电压Vin!因为UVLO只有500mv的回差电压,我在关断Power supply时(即Vin直接硬切断电源供给),Vin并没有直接掉到0,在一段时间内有个反冲电压,大于了UVLO,此时芯片判断符合芯片的启动条件,所以有个重启的过程!当Vin又下降到UVLO时,此时芯片彻底关断!所以想请教一下,怎么直接将Vin降到0?我不需要EN拉低,因为该芯片EN和SS共用,设置一拉低信号增加成本!非常感谢!

Hi,

你指的把EN脚欠压,接个分压电阻,直接在该引脚上接个10K的电阻可以吗?由于该芯片EN和SS引脚共用,不会影响软启动吗?

Hi

其实在正常的操作应用中不会出现你这类电源电压回灌的现象导致重启。

或者你可以减小输入电容看看,按照这个设计,实际的输入电容只要2个22uF+0.1uF即可(layout上靠近芯片Vin), 看看在断电后输入电压能否很开的被拉掉。同时注意连接PowerSupply到EVM板的导线,尽量短,低寄生电感。