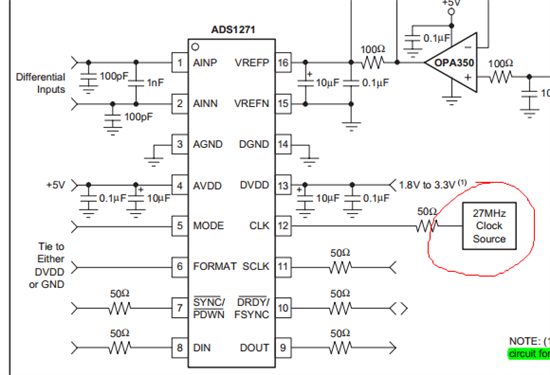

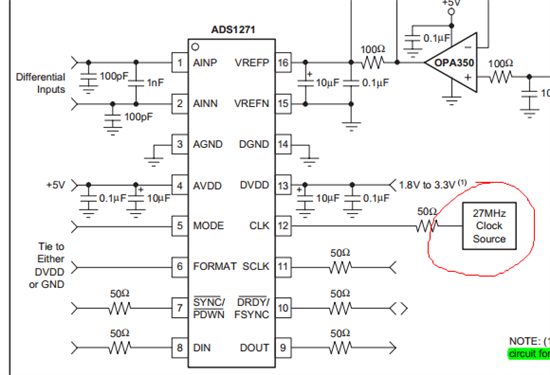

ADS1271的SCLK和CLK关系

时间:10-02

整理:3721RD

点击:

数据手册上指明:fsclk/fclk = 1, 1/2, 1/4, 1/8. 为什么要选取这些比例呢?

给CLK提供的时钟源为什么是27M?

说明内部有固有的分频系统. 应该没有啥多讨论的, 按照它的要求来设计时钟系统吧

数据手册上指明:fsclk/fclk = 1, 1/2, 1/4, 1/8. 为什么要选取这些比例呢?

给CLK提供的时钟源为什么是27M?

说明内部有固有的分频系统. 应该没有啥多讨论的, 按照它的要求来设计时钟系统吧