ADS1291 時脈 CLK SCLK

請問 如果ADS1291 使用 CLK = 2.048 MHZ

SPI CLK 可以使用 4MHZ 嗎?

您好,SCLK是要低于主时钟的,请按照datasheet第10页时序特性来配置SCLK。希望可以帮到您!

Andrew 您好

我的SPI CLOCK=4MHZ 所以 Tsclk = 1/4M =250ns

ADS 主時鐘 = 2.048MHZ 所以 Tclk= 1/2.048M =488ns

符合datasheet 第十頁的時序表

您好,ADC主时钟小于SCLK时,SCLK速率太快将导致接受的数据不正确,SPI接口本身难以判断收到的数据是否正确,需要在软件中处理。

Andrew 您好

我是用MSP430F5522 控制ADS1291

請問我可以把Firmware 貼給你嗎?

麻煩您再幫我看看該怎麼修改才能收到正確的數據

目前已經可以寫入/讀取 ADS1291暫存器

但是還是無法接到正確的轉換資料

謝謝您

您好,如果方便可以直接将程序以附件形式上传。谢谢您的支持!

3683.test.txt

以上是我的MSP430F5522韌體

我用 4MHZ 的 SPI CLOCK 配合 ADS1291 CLK 2.048MHZ

我發現我在寫入暫存器的時候 加入 for (i = 0; i < 10; i++); delay 就可以成功寫入/讀取暫存器

但是目前還是無法讀到正確的轉換訊號

您好,如果方便请上传一下测试的时序和转换结果。谢谢您的支持!

這是我的ADS1291 電路圖

AVDD = DVDD =3.3 V 使用內部VREF=2.4V

我是用Single-ended input . Common Votage =1.5V 在ADS1291 INIP 我是接到儀表放大器的輸出端(已經把位準拉至1.5V) ININ 接至1.5V

前端類比端 我將訊號放大3315倍 以及將準位拉至1.5V

然後我已經測試過類比端的輸出是沒問題的 也就是輸入ADS1291的波形是正確的

我這邊沒有測試的時序圖

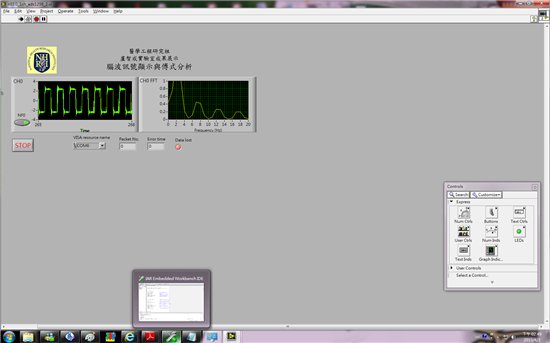

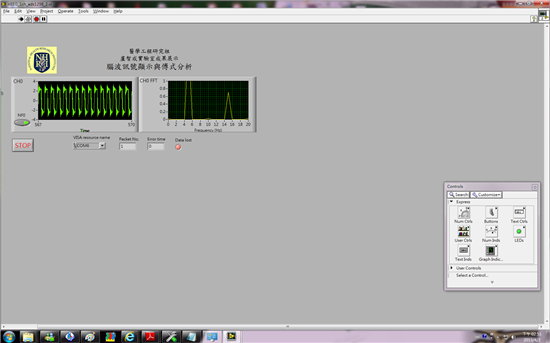

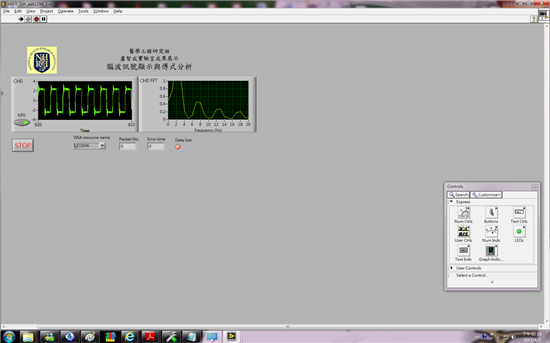

只有轉換結果圖 我使用藍芽傳輸 電腦端用Labview 程式接收

我先將弦波訊號分壓1000倍 再類比放大3315倍 再將放大後的訊號輸入至ADS1291

只有轉換結果

100mVPP 5HZ

100mVpp 10HZ

200mVPP 5HZ

200mVPP 10HZ

300mVPP 5HZ

300mVPP 10HZ

希望這些轉換結果能有所幫助

能早日找到問題

謝謝您

从图中观察,ADC是正常工作的,输出信号的频率出现错误。请参照datasheet28页公式(10)

For faster SPI interface, use fCLK= 2.048MHz and set the CLK_div register bit (in the LOFF_STATregister) to '1'.

不過 我是使用 SPI CLOCK=4MHZ

所以應該符合datasheet 28 頁 公式10

然後我的CLK_div也已經寫入1