ADS1298 SCLK 和DRDY信号问题

时间:10-02

整理:3721RD

点击:

各位工程师好,这几天调试ADS1298芯片时遇到一个奇怪的问题,请工程师看一下!

我将DRDY信号作为外部中断信号接到主设备(DSP)的GPIO引脚,设置的是当DRDY产生下降沿电平时,则启动中断服务程序,也即开始读取已经采集好的数据。

遇到一个问题是,DRDY信号是4ms的信号,但是SCLK的频率则为70ms;也即是说,DSP并没有检测到DRDY的每一个下降沿信号。请问这是怎么回事呢? GPIO是不是有周期检测的问题?

感谢工程师!

实际测试情况请见下图:

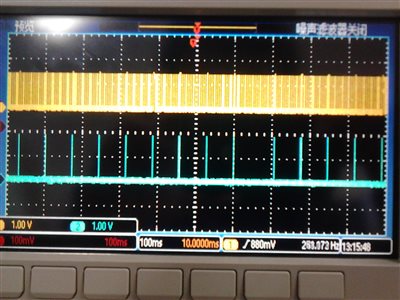

图01 黄色线是DRDY信号,蓝色线是SCLK信号(周期为70ms)

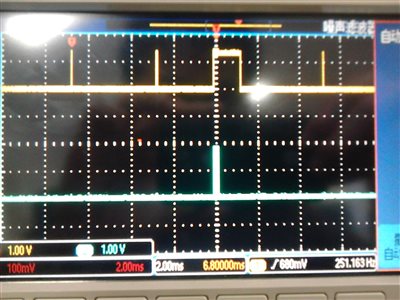

图02 黄色线是DRDY信号,蓝色线是SCLK信号(图中所示为发送数据时产生的脉冲)

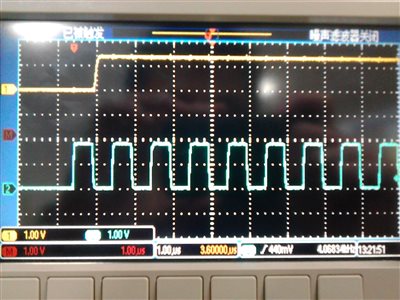

图03 黄色线是DRDY信号,蓝色线是SCLK信号(图中所示为发送数据时产生的脉冲,频率为1000khz)

可能模式设的不对吧。

把图也贴上来

感谢mmuuss586,请问能不能在详细介绍一下呢?

从图片上看,中断函数并没有对每一次的中断都进行处理,是不是每次进入中断后对数据处理的时间较长,导致再次进来的中断没有即使处理。

楼主:

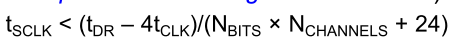

你好,请问你是配置在什么模式下读取数据。对于RDATAC模式下,对SCLK是有如下限制的

请确保你的SPI时钟满足该要求

感谢Janet Sun !

确实是每次进入中断后对数据处理时间较长,导致再次进来的中断没有及时处理。

原因是我的中断服务程序里有printf语句,将其删除即可!

非常感谢工程师的及时回答!