Systemverilog接口问题,求指教,谢谢~

`timescale 1ns/1ns

interface router_io(input bit clk);

logic [15:0] din;

clocking drvClk @(posedge clk);

output din;endclocking: drvClk//用来同步驱动

modport TEST(clocking drvClk);

modport DUT (input din);

endinterface: router_io

program test(router_io.TEST io);

initial begin

io.drvClk.din<=16'h2;

@(io.drvClk);

io.drvClk.din<=16'h4;

@(io.drvClk);

io.drvClk.din<=16'h7;

@(io.drvClk);

io.drvClk.din<=16'h9;

@(io.drvClk);

io.drvClk.din<=16'h3;

@(io.drvClk);

#50 $finish;

end

endprogram: test

module dut(router_io.DUT io);

initial begin

$monitor("@%0t:io.din=%h",$time,io.din); //检测变化;

end

endmodule: dut

module top;

bit clk;

always #5 clk=!clk;

router_io io(clk);

test t1(io);

dutd1(io);

endmodule

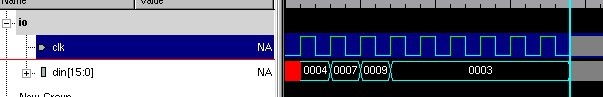

就是用了接口,同步驱动DUT,问题是:仿真结果是 4--7--9--3,为什么偏偏红色那个2 没有驱动进去呢?仿真结果如下:

请指教啊,万分感谢~ 为什么第一个就没有了呢?好奇怪啊

把第一个赋值语句写到program外面试试?

你使用的是时钟块同步信号,在始终上升沿采值,第一个2在时钟沿之前,当然不会采到值啦,试一下

@(io.drvClk);

io.drvClk.din<=16'h2;

谢谢,就是这个问题,改正顺序就对了。我还是没理解我的写法为什么不行,即先把数据准备好,再等上升沿的到来去采准备好的数据和正确的--先等上升沿到来再送数据。我本意是先把数据准备好了,然后等着时钟上升沿到来。就像如果只写下面一个驱动,也是能输出2的,也就是这个数据送了出去,这个怎么回事呢?io.drvClk.din<=16'h2;

@(io.drvClk);

#15 $finish;

//////////////////////////////////////////////////////////////////////////////////////////////////是不是意味着 以后搭建测试平台时不能像红色这种写法来送数据,这样会丢失第一个数据

for(int i=1; i<6; i++) begin

io.drvClk.din <= i;

@(io.drvClk);

end

而应该尽量用蓝色这种写法:

for(int i=1; i<6; i++) begin

io.drvClk.din <= i;

@(io.drvClk);

end

我的理解对不?请指教谢谢~

你的2值肯定不满足一个时钟周期的长度,这样是不会被采样的。你可以参考systemverilog讲clocking的部分

你可以看一下《测试平台编写指南:SystemVerilog验证》中的关于时钟块介绍,以及信号采样的相关章节(好像是在第四章,忘记了),对输入信号的采样是默认在时钟沿之后的一个时间单位?具体不记得了

谢谢

thank you

感觉验证真是个精细的活啊,要求好高啊

在始终的有效沿驱动同步接口信号, 2在始终有效沿之前,所以没有没踩到