sv中两种延时区别:a<=#10 b 和#10 a <=b;

时间:10-02

整理:3721RD

点击:

always @ *begina <= #10 b; end

always @ *begin#10 a <= b; end

第一种可以正确延时,第二种就比较诡异了,求指教到底啥区别呢

always @ *begin#10 a <= b; end

第一种可以正确延时,第二种就比较诡异了,求指教到底啥区别呢

假如B当前值变为1,5个时间单位后变为2.

第一种:将B的值(1)10个时钟单位后赋给A;

第二种:10个时间单位后将B的值(2)赋给A;

总结:第一种是将B的当前值延迟10个时间单位后赋给A;第二种是延迟10个时间单位后B的值赋给A;

第二种按理解是这样的,可是仿真结果不太一样啊。

从实际芯片设计的案例来看,第二种的写法意义不大,而且很容易引起仿真的奇怪问题

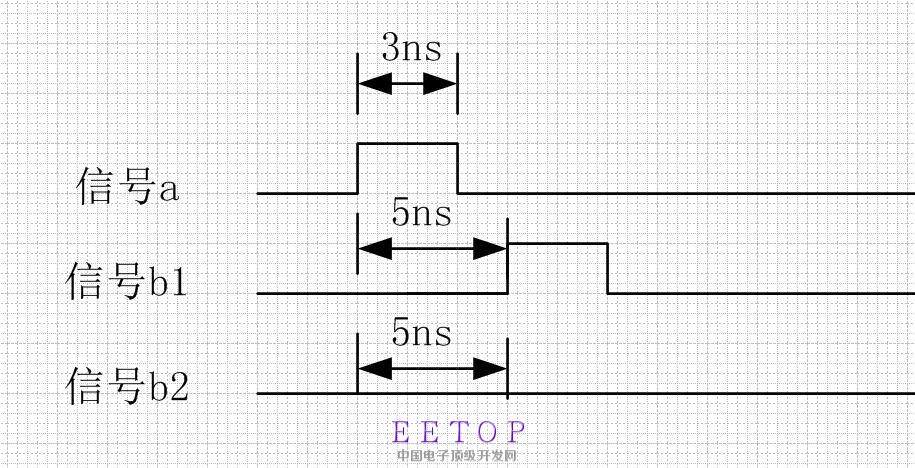

always @ *beginb1 <= #10 a; end

第一种是真实的延迟处理,直接将信号a延迟10赋值给信号b1

第二种是可以按照以下代码理解:延迟10时间单位后,将a当前时刻信号值赋值信号b2

always @ *

begin

#10;

b2 <= a;

end

示意图

如果b的默认值为0b在5ns时变为1

b在6ns时变为2

b在7ns时变为3

则:a<=#10 b#10 a <=b

a在15ns时变为1a在15ns时采集b的值即3

a在16ns时变为2a一直保持3

a在16ns时变为3

前面已经说的很明白,同一2l,5l

1)描述传输延迟,可以理解为信号在路径上传输花费时间到达目的;

2)描述惯性延迟,可以理解为信号延迟一段时间开始传输,下于这个时间的毛刺都会被吸收掉;