systemverilog 中的virtual都是什么意思?

由virtual所声明的内容可理解为一个模板,后续的例化和引用可在这个模板上进行增加或修改,这样就呈现出特定的内容或特性。不同的引用或修改实现不同的对象、接口和方法。

这样就很方便的实现了面向对象的特性,即多态实现随继承对象的不同而不同。

说明:

1、virtual interface:定义一个interface,且实例化多个后,如果没有定义virtual,则在任何一个实例中修改了某个信号值,在其他实例中都会受到影响。如果定义了virtual,则每个实例独立。

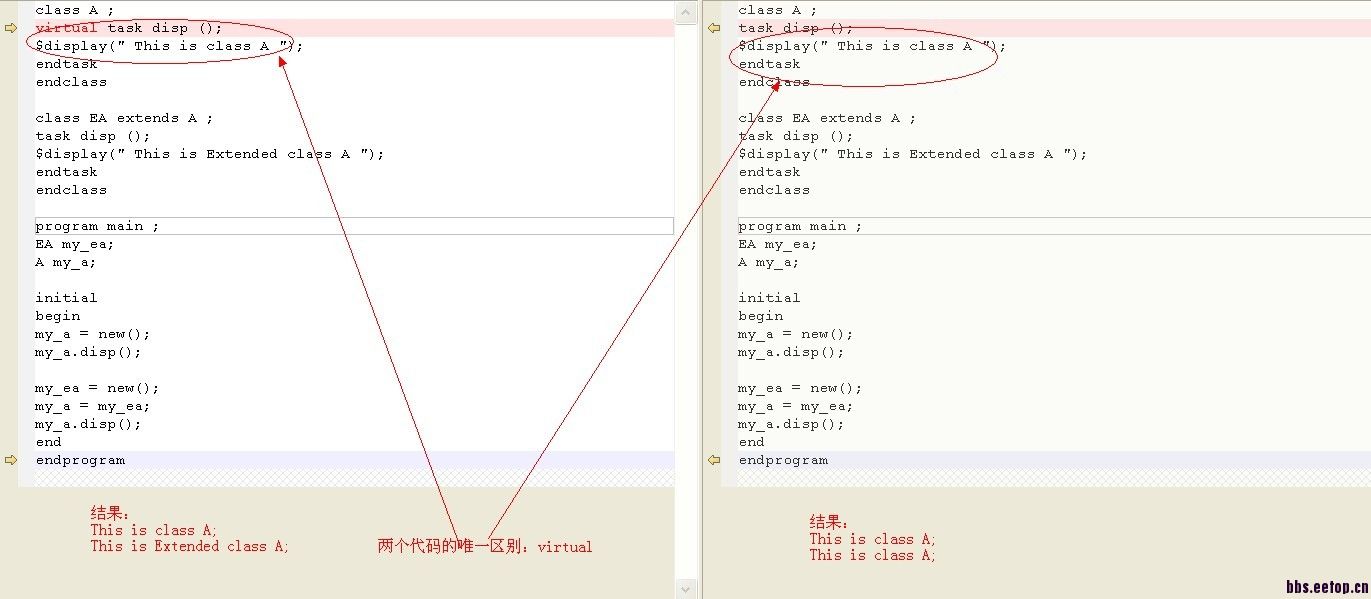

2、virtual function/task:用于OOP思想的继承使用。当定义了virtual时,在子类中调用某function/task,会先查找在子类中是否定义该function/task,如果没有定义该function/task,则在父类中查找。未定义virtual时,只在子类中查找,没有定义就是编译错误。

3、virtual class:从未用过,等待牛人解答

用法:

1、virtual interface:如果该interface只有一个实例,可用可不用virtual,有多个实例,需要virtual。更好的办法是,都加上virtual。

2、virtual function/task:如果该class不会被继承,则所有的function/task都不需要加virtual。如果该class会被继承,则用户定义的function/task(除了new()/randomized()/per_randomize()/pose_randomize()以外),都应该加上virtual。更简单的做法是,在用户定义的function/task都加上virtual是不会错的。

3、virtual class:期待牛人解答

多谢解答!

解答的很清楚。多谢

virtual 还是很有用的,是面向对象思想的一个重要特性!

1、virtual interface:

interface 和 module是一样的, 都是静态的变量, 也就是在程序开始时, 内存中就有了其实例. 但virtual interface只是申明一个handle, 就好像一个指针一样, 可以再程序进行中进行construct, 所以class里必须是virtual interface.

2、virtual function/task:

你的意思是不是用classname::taskname()调用时, 有virtual, 但是子类中没重载的话, 不会报错?

一般申明了virtual, 就可以重载, 这也是new为什么不能virtual的原因, 否则被子类重载了, 那用父类的handle new的时候, new出来是啥啊?

3、virtual class:

虚类只用来定义类的格式, 和成员的名字, 参数, 不能被实例话, 只能被重载, 用于在项目中定义一些标准的类, 例如driver类, 这样大家extend出来的driver的基本的格式都是一样的, 易读易理解. 在virtual class里的方法最好使用 pure virtual 修饰, 叫做纯虚方法, 也是用来定义方法的名字和参数列表的, 方便大家统一名字.

解释得很清楚

非常的谢谢!

3楼说的还算明白,多实践就知道了

明白了啊。

明白了。

学习一下

解释的非常清楚,受教了

解释的很清楚!谢谢。

说的很明白,比我理解的好,学习了

这个例子举得非常好,多谢,受教了!

头像不错

关于virtual interface,我不是很明白你的解释。

- `timescale 1ns/10ps

- //====interface

- interface inv_if();

- logic in, out;

- endinterface

- //====module

- module inv(inv_if t_if);

- assign t_if.out = !t_if.in;

- endmodule

- //====top

- module top;

- inv_if intfc1(), intfc2();

- inv inv1(intfc1);

- inv inv2(intfc2);

- virtual inv_if t_if;

- initial begin

- intfc1.in = 0;

- #1;

- $display("@%0t : intfc1.in = %d, intfc1.out = %d", $time, intfc1.in, intfc1.out);

- $display("@%0t : intfc2.in = %d, intfc2.out = %d", $time, intfc2.in, intfc2.out);

- #5

- $finish;

- end

- endmodule

如果代码如上的话。没有virtual的interface inv_if例化的两个intfc1和intfc2的值的变化都不是相关的。所以我不太明白你说的virtual和非virtual在使用上的区别。

建议了解一下C++

virtual class不能被实例化怎么理解?可以声明,不能new?

解释的很清楚,不过不是太懂。

果然學習到知識

mark

学习了

回答的好具体,3Q!