verilog 时钟边沿的采样

时间:10-02

整理:3721RD

点击:

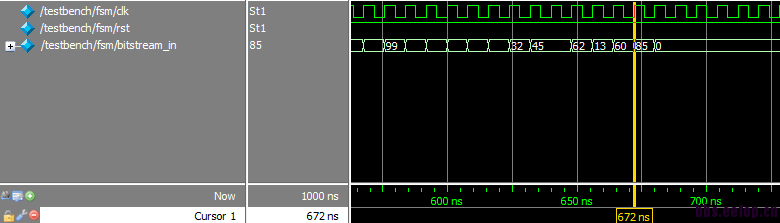

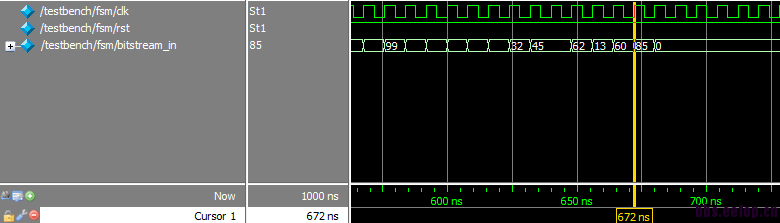

编写了一个状态机,有三个不同的信号,于是写了三个always块(敏感列表相同,同为电平敏感),但是发现时钟在同一个仿真时刻(时钟上升沿)所采到的信号值不同,具体如下图

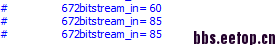

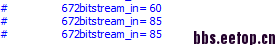

672ns时采到的bitstream_in的值应该是85,但是其中有一个always块采到了60。

求问原因及解决方法

672ns时采到的bitstream_in的值应该是85,但是其中有一个always块采到了60。

求问原因及解决方法

时钟上升沿的时候,数据恰好处于变化的时刻,这种情况下,有时候还真不好判断。

给你个建议,在所有的时序逻辑前面加一个“#1”的延迟,那么时钟采样的时候一定会看得准确。

这个对仿真很有帮助,这对综合没有影响,因为DC综合的时候会自动的去掉这些#1的延迟。

譬如:

你以前写的是

a <= b;

你换成a <= #1 b;

可以试试这种写法,看结果如何

仿真时在Interface里加个clocking模块,应该可以避免这种race condition

这样写在Xilinx ISE里面综合不会通过的吧?我是要烧到FPGA上面的,这样写恐怕不行。

能说的详细一些么?什么叫在Interface里加一个clocking模块?

Clocking blocks 主要用于testbench,控制信号时序同步。即信号的同步时序与时钟相关。在clocking block内的信号将被同步驱动或采样,以确保testbench和signal在正确的时间点进行交互。

信号延时不一样吧,加寄存器?