NC-Verilog 后仿所遇到的问题

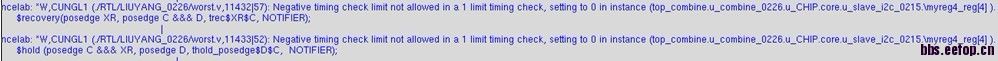

最近在用NC-Verilog 做后仿时,发现了一些问题:ncelab top -access时,它报了大量的warning,大致是一个原因的warning:

图片没有传好,几个关键字是:Negative timing check limit not allowed in a 1 limit timing check, setting to 0 in instance.

开始上网查了资料,说是负延迟,按所说方法(-neg_tchk或者是-noneg_tchk)均没有用。

请问它的warning是不是说:NC-Verilog将负延迟变为0 了?该怎么解决呢?

请各位高人指教!不甚感激!

没遇到过,但个人感觉可能后端网标时序上是否有点问题,做过PT吗?

恩,pt过了

哪报警的地方会不会是异步时序,若异步则可不予理会。

应该是时序问题。

我做的都是异步复位,可能跟这个有关系。现在加了一个同步释放的电路,还没有做完后端,做完后再看下后仿结果。

可能是的,做的是异步复位,但是为什么异步时序不管它呢?谢谢!

异步复位的复位时间很可能跟你的系统有关,如果你的TB确实和系统应用一致,则需要解决。

若果异步复位时间是自己随意写的,该错误很可能是个假错,可以不予理会。

谢谢,我再去查查。

"异步复位的复位时间很可能跟你的系统有关,如果你的TB确实和系统应用一致,则需要解决。

若果异步复位时间是自己随意写的,该错误很可能是个假错,可以不予理会。"

您好!现在我的问题仍旧没有解决,还得跟您请教一下:您说的“你的TB确实和系统应用一致”这句话是什么意思?一致主要体现在哪些方面?时钟周期?(现在TB的时钟周期和后端约束差不多)

谢谢!

TB中RESET到来和结束的时刻与时钟的相位关系是否与系统应用中的RESET到来和结束的时刻与时钟的相位关系一致,不过一般情况下很难做到一致,所以经常忽略。倒是高速电路中专门有一个模块来解决该问题(据据说英飞凌等公司就是这么做的),具体怎么解决我不是很清楚,你需要找资料看看。

啊,谢谢谢谢!确实不知道怎么样做个一致呢,不过我这个频率相当地低——4M,应该可以忽略吧?