请教标准单元库的使用

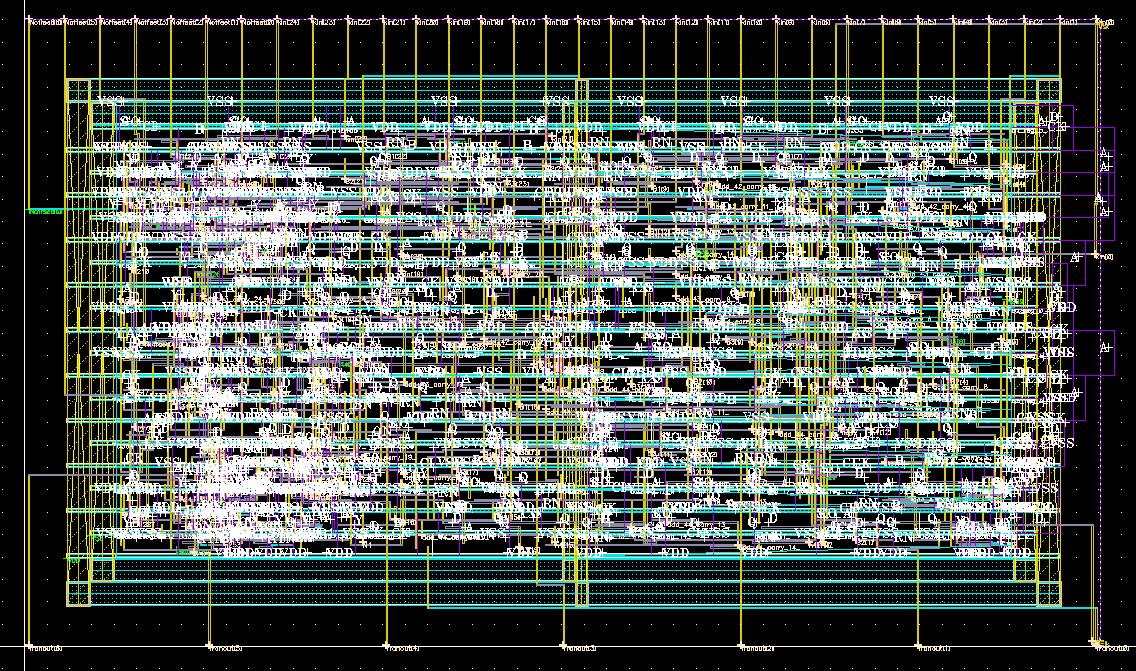

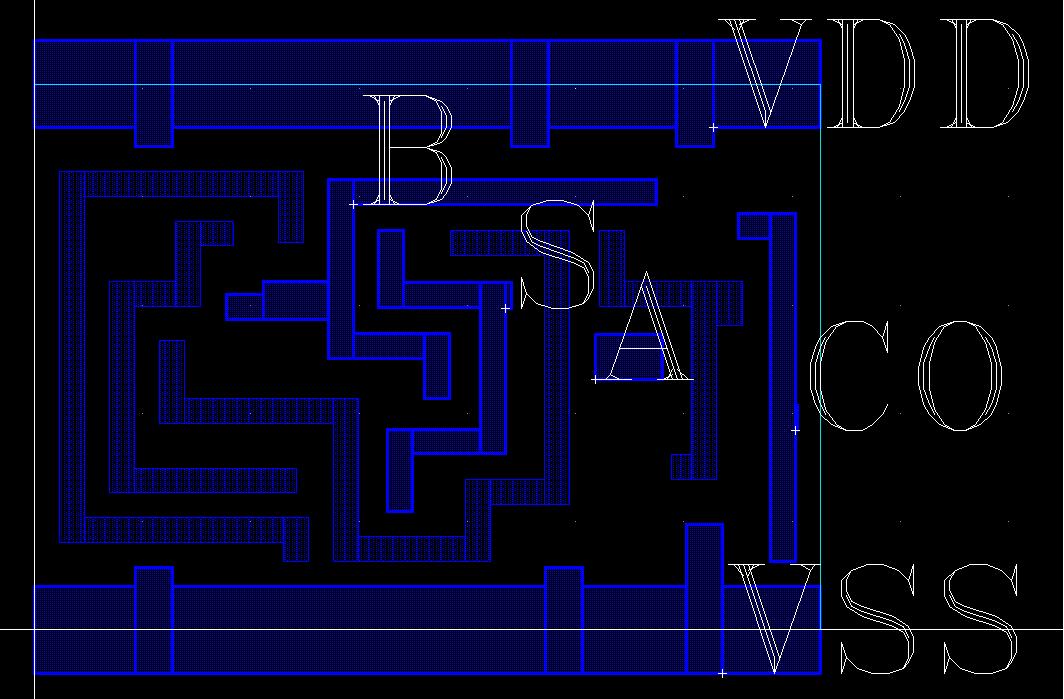

我最近用DC做完逻辑综合后,通过SOC encounter布局布线后,再把布局布线的结果存为GDSII及DEF文件以导入到Virtuoso里面做后续的版图处理,可是当我导入这些文件后,layout始终没法显示,如下图1所示,在版图里面只能显示两层金属,标准单元库里面的信息都没法显示出来,在导入版图之前,我已经把标准单元库里面的Symbol lib加入到Cadence里面,然后import LEF文件生成对应各个Symbol的layout及abstract View,但是这些View看起来也是很不正常,如图2所示,标准单元内部显示也是有问题的,这不知道是不是在导入LEF文件时产生的layer map的问题?

想请问下,关于标准单元库的应用的具体流程是怎样的?我们应该如何把这个库加入到Cadence里面,保证显示正常,在导入DEF及GDSII文件时,要注意些什么问题?

另外,我在导入DC生成的门级见表verilog的时候也出现了问题,导入后只能显示几个pin(这些pin也不是我内部定义的),在导入Verilog的时候就没有出现导入的过程,导出的那个Schematic里面就没有任何标准单元库的Symbol,请大家指教,谢谢。

thank you very much. ....

thank you very much. ....

标准单元

我要这个标准单元

怎么没人回答啊我也很想知道啊

thank you very much!

Symbol库用于电路设计

LEF库用于布局布线

GDS用于布线后的物理验证用,作为Ref Lib导出GDS

一般讲为了导入设计必须先准备好单元库(schematic、symbol或layout),这些单元库必须与特定的工艺库关联,virtosor环境要进行设置,这样单元库就没有问题了。其次在导入时必须正确的指定单元库和工艺库,才能正确的导入。有时导入不成功可以将导入设计的库手动链接一下工艺库也可以好。

估计你的情况是后者

你没有将std cell的gds merge进来。import std gds到virtuoso中design的库中试试。

dingding

标准单元的gds库没加进来。

顶啊 啊

想学习。

9楼说的对。你从encounter导出来的gds设定的layer map只是你走线和via的,它需要一个与std gds merge的过程才能完全显示你的标准单元版图。现在encounter的streamOut有个选项是-merge,你可以把std gds还有其他一些硬核的gds都包含在这个选项的路径下,这样导出的gds就是包含所有信息的,在virtuoso导入后可以直接看到了。祝好运

14楼说的非常详细了

高人指点一下吧

我会一直关注这个帖子的。我的问题也是这样

我也遇到了同样的问题,不过我用的是资版的库,可能的原因是库没设定好,或库不全(只有外部属性),

我也想知道这个问题的准确回答,谢谢.

14楼!

你好,我现在也遇到跟你一样的问题。然后我按照你之前发的帖子的回帖中解决的办法试了下,merge了一些调用过的单元库的gds,有一些变化,在virtuoso里面,之前看不到的相应的单元库变成了常见的红框里面一个叉叉。不知道是为什么原因? 是不是因为我在cadence的icfb里面没有引用标准单元库的原因么?那如何在icfb中引用呢?

bd,我也想学学~

同意楼上的

真有意思

xue xi le !

学习。

看不懂

感谢分享,仔细看了下,我们以往出gds的脚本里,streamOut也是加了-merge的option的,set merge_list “”, streamOut -merge ${merge_list}

,所以没出现过小编的问题

学习了

我下载了一个SMIC 0.18um 的标准单元库,里面有standard和io两个文件夹,但我不知到怎么添加到setup里去,有没有前辈能指导一下?

学习了