最近做综合所遇到的问题总结及思考,希望大家多多参与

最近做综合所遇到的问题总结及思考

设计中存在多个时钟输入,而几乎每个时钟都有经过分频传递给子模块做时钟,而且每个分频时钟都经过了门控,所以这是我遇到的时序最为复杂的最难处理的设计了。

现在就设计中所存在的各种case做逐一分析,以求能做到书本理论和实际设计向结合。

Case1

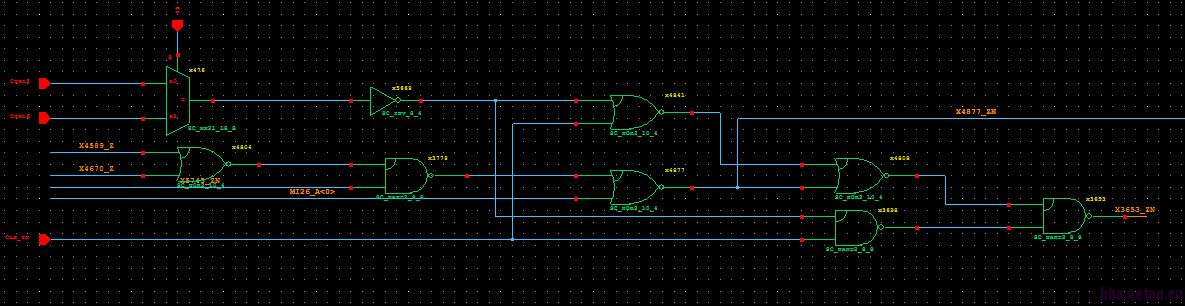

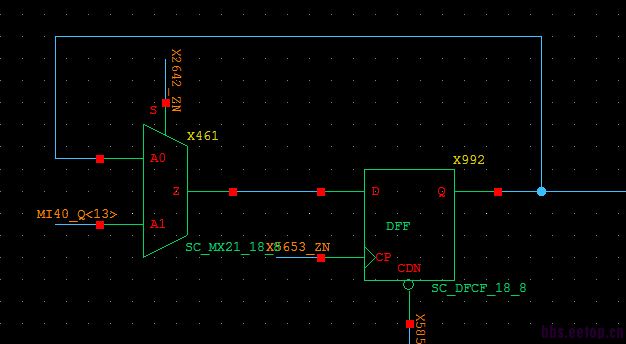

门控时钟

这即是一个门控时钟的例子

时钟CLK_IN经过多个控制信号的逻辑控制之后才输出给时序模块,首先声明,设计中绝大部分门控电路都是手工的,即

Assign clk_gated=clk&enable;

Always @(posedge clk_gated)

Begin

…

End

综合的时候的处理是

Create_clock–name –p [get_ports CLK_IN]

我的问题是,所有手工的门控时钟是不是不被DC理解为门控时钟呢,因为我的所有门控时钟都是手工的,没有条用ICG单元,也没有用一个时序器件DFF和一个与门结构,最后使用report_clock_gating命令却有下面的结果,被门控的寄存器为0,这是为啥呢?

Clock GatingSummary

------------------------------------------------------------

|Number of Clock gatingelements|0|

|||

|Number of Gatedregisters|0 (0.00%)|

|||

|Number of Ungatedregisters|531 (100.00%)

|

|||

|Total number ofregisters|531|

------------------------------------------------------------

我在这里有一个疑问,书上介绍说可以采用

Set_clock_gating_style

Replace_clock_gates

命令来将手工门控时钟取代,在这里有没有这个取代的必要,如果取代的话,都有哪些门控时钟进行了取代操作,在命令中没有指定哪些时钟被取代,哪些不取代;如果没有取代的必要的化,那就是下面的问题,就是如何保证门控时钟的时序问题

我用了下面的命令

set_clock_gating_check -setup 0.3 -hold 0.3

这里留有的余量都是0.3,这个值到底够不够?

下面的warning可能跟这个check有关

Gated clock latch is not created for cell'MI96/X6187/C9'on pin 'B' in design 'DIGITAL_LOGIC1'. (TIM-141)

Information: Generated Clock (X1129_Q) hasnon_unate sense on master source pin. (TIM-193)

No controlling value could be found for theclock gating cell 'MI170/X865/U1' for the clock pin 'A'. (TIM-128)

Warning: A non-unate path in clock networkfor clock 'CLK_IN' from pin 'MI170/X865/U1/Z' is detected. (TIM-052)

所有这些warning是不是可以waived?

Case2

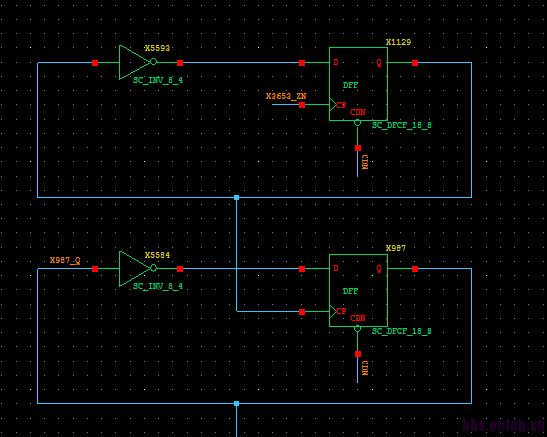

Generated 时钟

这是一个典型的时钟分频的电路

我用的命令如下

create_generated_clock-name X1129_Q-divide_by 2-source[get_pins MI25/X1129/CP][get_pins MI25/X1129/Q]

create_generated_clock-name X987_Q-divide_by2-source[get_pins MI25/X987/CP][get_pinsMI25/X987/Q]

分频时钟这块没什么大问题,就是想强调一点,-source最好是DFF的CP端,这样就能保证分频后的时钟和驱动时钟的相位关系没有差错

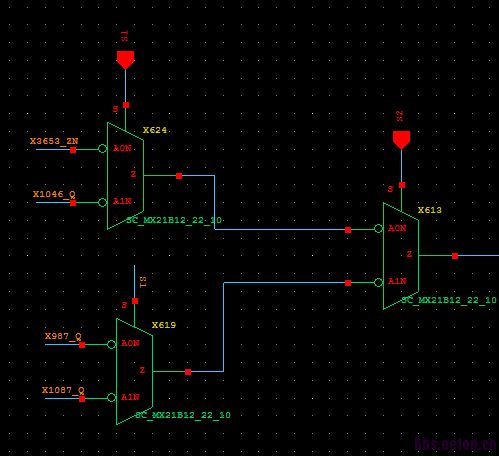

Case3

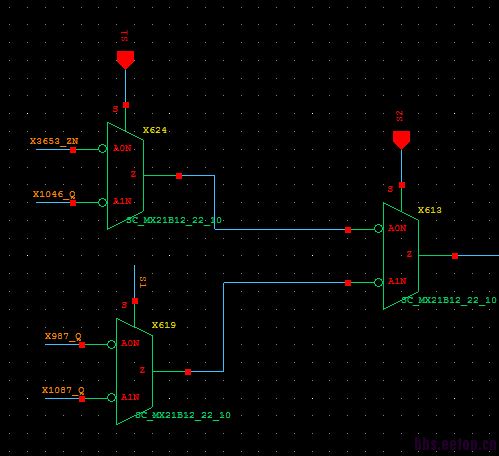

多时钟情形

下面电路时master clock以及分频时钟的选择电路

我见过有在网上建议使用

Set_case_analysis命令的

我在这里使用的是

set_clock_groups -logically_exclusive

-group {CLK_IN} -group {X987_Q} -group

{X1046_Q} -group {X1087_Q}

大家给个建议,到底使用哪个比较好呢?

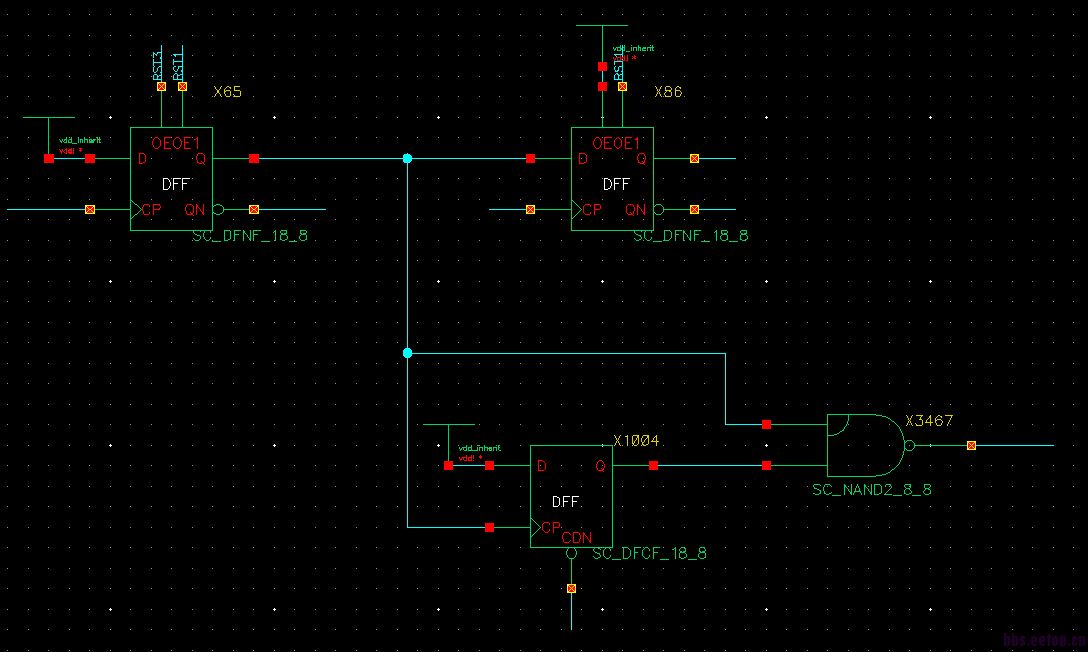

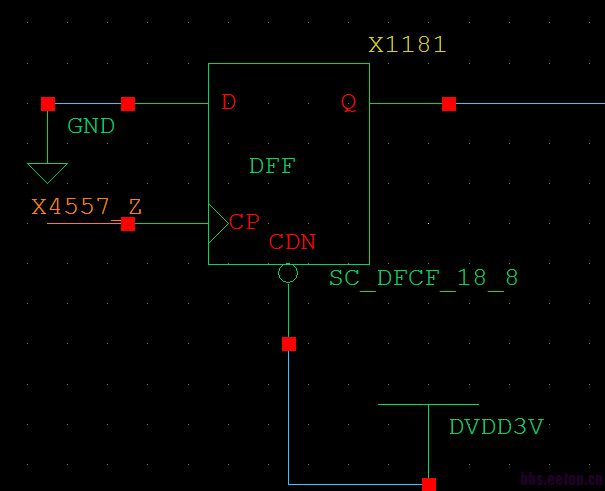

Case4

这个情形我是没见过,孤陋寡闻了。

大致介绍一下,这里的时钟端其实不是时钟信号,而是一个reset信号,大致就是为了上电复位的时候读取一个笃定的值作为地址或者什么ID之类的不变量,请问这种情形是如何处理?难道是在reset端创建一个clock吗?

我是在这个地方创建了一个clock,但是工具最后提出来一个warning

Warning: The set_dont_touch_network command is used for clock X4557_Z, for which no sources are specified. (UID-997)

Case5

有点类似于上面的情形

但是这里的前级时钟的确是一个时钟信号,但是触发器的输出又做为一个时钟信号驱动下级触发器,请问这里如何create_clock以及如何create_generated_clock

Case6

Timing loop问题

Warning: Disabling timing arc between pins 'CLK' and 'QBAR' on cell 'MI51/X992/Q_reg to break a timing loop. (OPT-314)

工具辨认出timing loop并且自动打断了,这里需要人工干预什么吗?

尤其是CASE1,请大家多多指教

设计没给出解释么,

case4 CDN接1,不reset的信号也能用?

case5 从逻辑上像是reset后产生one cycle的pulse

case6 timing loop要查RTL吧,FM难道过了? 或者leda lint 都过了?CASE4 应该是可以用的,寄存器输出就是作为一个固定的值,即便不reset的话,也应该是0输出吧,有了一个clk信号,输出更能固定在0,我是不明白,这个地方还有没有必要对时钟信号create_clock?

在不reset的时候,这个FF输出0,有没有风险? 如果FF是两个latch的结构,那么你clk端一开始是高电平还是低电平?会不会对Q有影响?另外,就算电路是定态,后仿会有X吧

非标准同步设计,clock tree也不用平衡,clock 也没什么load, 我觉得没必要create clock 了,再问问这边小编吧,话说陈涛老大很久没有出现了啊case1 我记得DC有命令来识别cg的 看看结果是不是能给些提示啥的 工具识别不出来会不会是组合逻辑太复杂 用了AO这种器件之类?不能替换可能还和库有关

case3 应该差不多 只是logic exclusive 能省几行字 另外sta能在一个session

中都分析了

case4时钟随便设 不用balance

case5 没看懂 为啥有loop? pin的名字好像对不上?为啥是正在virtuoso环境里面呢, 模拟的人自己搭的clkgen 模块?

case1提示warningGated clock latch is not created for cell'MI96/X6187/C9'on pin 'B' in design 'DIGITAL_LOGIC1'. (TIM-141)

Information: Generated Clock (X1129_Q) hasnon_unate sense on master source pin. (TIM-193)

No controlling value could be found for theclock gating cell 'MI170/X865/U1' for the clock pin 'A'. (TIM-128)

Warning: A non-unate path in clock networkfor clock 'CLK_IN' from pin 'MI170/X865/U1/Z' is detected. (TIM-052)

门控部分的组合逻辑确实有些复杂,但是也都是简单的与或门组成,是不是需要在每一个控制信号上指定有效电平,这个怎么弄呢,感觉不太会,请指教

如果不用 replace_clock_gates,而是使用insert_clock_gating,也是提示同样的warning,工具识别不出来

综合的结果与手工搭出来的电路进行比较,确保电路功能一致继续顶起

请教一下,我也碰到了这个问题,能详细说一下问题所在吗?谢谢

warningGated clock latch is not created for cell'MI96/X6187/C9'on pin 'B' in design 'DIGITAL_LOGIC1'. (TIM-141)我想,综合的时候会不会根据代码风格自动生成clock gate(ICG),如果自己手动加要是那种std_cell