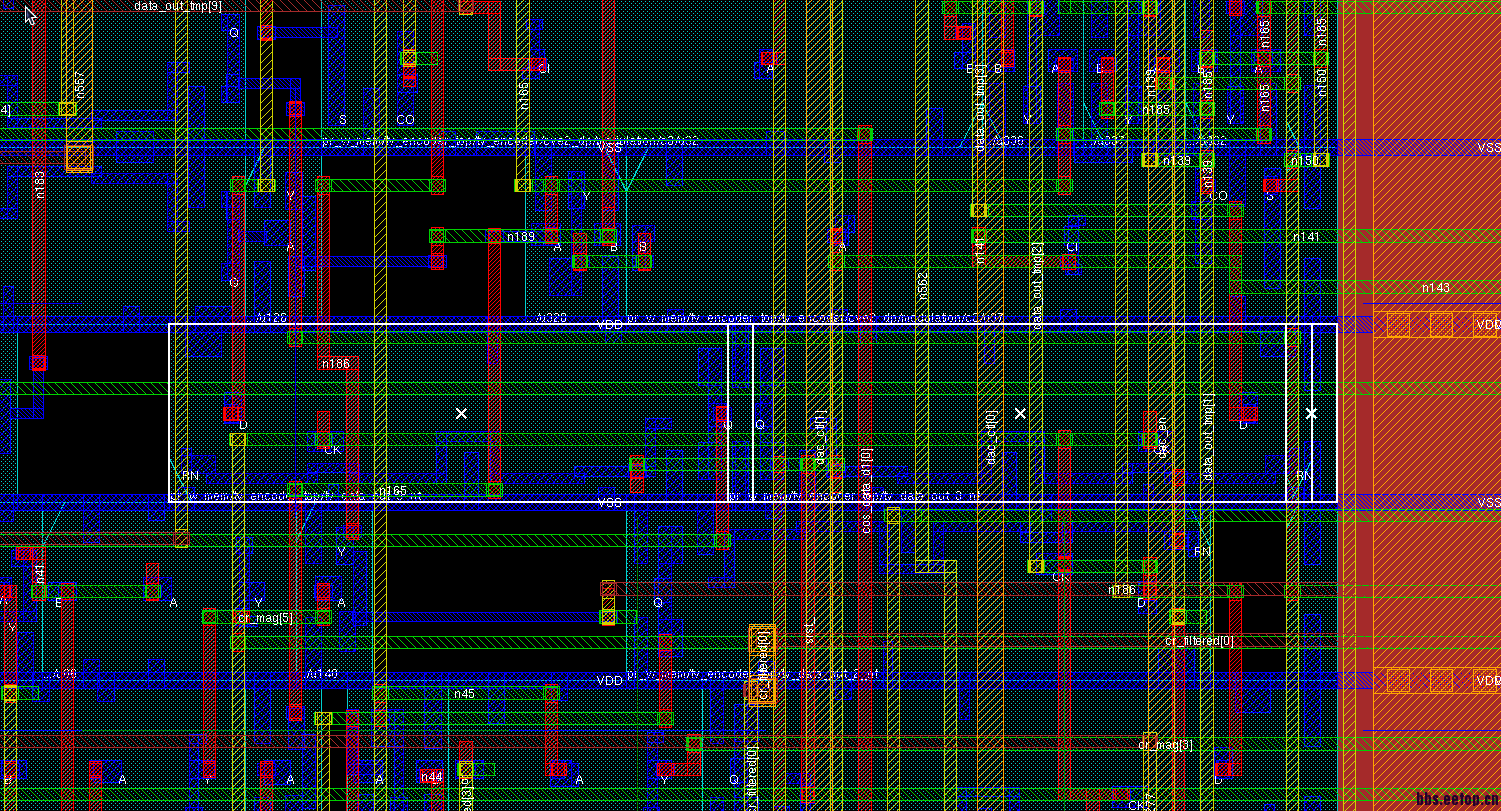

为什么encounter,place之后会有器件重叠啊?还有就是standcell的metal1都有DRC问题

时间:10-02

整理:3721RD

点击:

为什么encounter,place之后会有器件重叠啊?还有就是standcell的metal1都有DRC问题?

工具提示metal1有DRC问题,但那是standcell的metal1 呀,我把metal1的引线删掉打算再连上时,就再也连不上原来的位置,总是在原来的位置偏左或偏右,总是对不准,是什么原因啊?是不是要设置栅格大小,该在哪里设置要设置多少才合理啊?

(1)Routing前,先用Refine Placement, 面積不夠時,cell會重曡.

(2)cell外框和metal都要在pitch上,有些routing太緊,一定會有drc,要手修.

Good luck.

面积肯定是够的,都剩下很多空的地方了,至于cell外框和metal都要在pitch上,这个该怎么理解?是不是tech lef file上面定义的pitch

ecoplace下,

是LEF檔上的外框layer.

问题根源找到了,是tech lef定义值导致的

谢谢,问题解决了

涨涨人气

赞一个!

overlap 也是 techlef 导致的?

这个确实是tech lef导致的,但是怎么解决呢?这个lef文件也不能修改啊

请问前辈最后是怎么解决的阿

可以具体解释一下问题是咋解决的吗?碰到了类似的问题