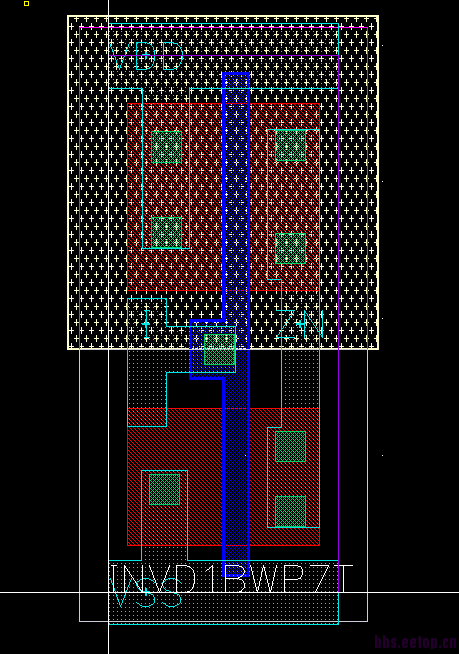

感觉标准单元不对,大神帮忙看看

采用这些标准单元进行设计,到DRC的时候出现了上万个下面的关于闩锁的错误:

LUP.6 { @ Any point inside NMOS source/drain space to the nearest PW STRAP in the same PW <= 30 um

@ Any point inside PMOS source/drain space to the nearest NW STRAP in the same NW <= 30 um

@ In SRAM bit cell region, the rule is relaxed to 40 um

PACT_CHECK_NON_SRAM NOT NSTP_OS

PACT_CHECK_SRAM NOT (NSTP_OS OR NSTP_OS_SRAM)

NACT_CHECK_NON_SRAM NOT PSTP_OS

NACT_CHECK_SRAM NOT (PSTP_OS OR PSTP_OS_SRAM)

请问各位前辈:(1)这个错误是不是由于阱悬空引起的?

(2)如果是,该怎么修改?因为所有的标准单元都有这个问题,所以不可能一个一个修改,应该在PR的时候怎么处理呢?

注:在PR完成后,我在encounter工具里做了DRC的检查(我知道这个不完全正确)

好好看手册,这库是要自己家TAPCELL的吧

见到有人用我做的库真亲切啊

小编 你忘了撒TAPCELL了

什么?请前辈告知具体原因!感激不尽!TAPCELL是在标准单元库里面吗?还有撒TAPCELL是在P&R的哪个阶段?

多谢多谢!

我在仔细看看标准单元手册。请问前辈这个TAPCELL的作用是什么?应该怎么添加?(我是用的encounter做的自动P&R)

感激不尽!

TAPCELL 就是提供井电位的,每60u左右撒一个,placement前撒进去

encounter有专门的命令做这一步

这套库是我n年前的作品 哈哈 有点小兴奋

小编 加个Q 呗 95428743注明标准单元

奥,ok.我试试,多谢指导!

好的,已加了。刚看到

addwelltap,

t018 当然是很老的库了,哪年了,都

这都敢做芯片,这是那家公司,管理出大问题了。

Floorplan就应该加tapcell了吧...

对,我这次就是这么做的。先试试看

在校学生。

实验室做的可能都比较落后吧。更注重功能结构实现和方法的创新。公司可能更注重产品性能,采用更先进的工艺。

台积电的大神啊,膜拜一下

也很可能是ARM那边的, 呵呵 Artisan

cell name一看就是TSMC标准的命名规则

ARM不是这样命名的

n年多少年? T在0.18um上早期是Artisan的库,很成熟,为何自己还有开发库? 0.18um有必要做tapless的库吗?

可以把stdcell的track做少,节省面积。

小编最后是怎么解决这个问题的啊?我也出现了这个问题。

小编最后是怎么解决这个问题的啊?我也出现了这个问题。

我忘记了,好像是要撒TapCell;我已经不做这行了。sorry

前楼有说,innovus有专门的命令来撒tapcell,间隔一定间距。

很棒 感谢分享

小编 做哪行去啦?