后端面试--每日一题(061)

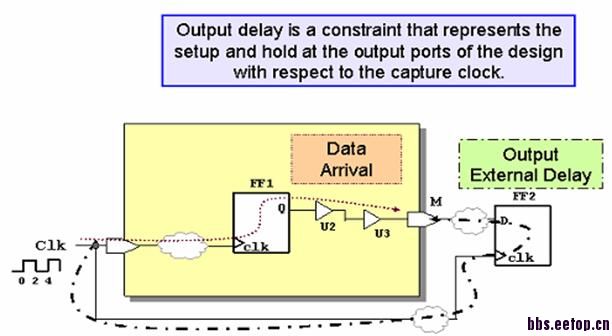

picture is a block design.

1) how many timing path?

2)after placement, the worst setup and hold slacks are all 0ns.next building clock tree. Assume the tree is balanced and theinsertion delay is 0.2ns in WC, 0.1ns in BC. Then checking timingagain. Is there any timing violation? how many and how muchviolations there is? is it real? how to fix it?

上图是一个block (不是chip),问

1)有多少timing path

2)place之后,假设setup和hold都正好为0ns,然后插入时钟树,树的完全平衡的,WC的时钟树insertiondelay是0.2ns,BC的insertion delay是0.1ns,这时做STA,会看到timingviolation吗?有多少条violation,各违反了多少ns?他们是真的吗?如何解决?

难度:4

覆盖了基本的STA类型

有难度

对于我这种新人来说就更加有难度了

有4条timing path

CTS后setup在reg2out path 有violation

hold在in2reg上有violation

但是这些violation是假的。需要调整input output的约束。

各有多大的violation?

如何调整?

in2reg: hold -0.2

reg2out:setup -0.1

如果IO部分是由real clock来constraint的,在做完CTS之后用update_clock_latency 而不是set-propagated_clock,如果是virtual clock constraint IO,那就得先设set_latency_adjustment_options -from clk -to Virtual clk,再update_clock_latency

hold -0.2, setup -0.1 对吗?

没有试过你说的方法,不敢说对错

这是一道由浅入深的问题,第一问很简单,答错的话,后面就不用问了

CTS后,是否有违法,违法多少,是中等难度的问题,答对的话,说明有block level P&R的经验

如何修复违法是有些难度的问题,

简单的回答是在input delay上加clock insertion delay的值,在output delay上减去clock insertion delay的值

但是当有上千个input和output port时,做起来比较麻烦,

有个非常简单的方法,想到了,就是满分!

错了,hold 是-0.1

setup是-0.2

见笑了

set_input_delay -network_latency_included,

set_output_delay -network_latency_included,

对吗,陈小编?

那个简单的办法是:

设一个虚拟时钟,与clk同频同相,

把所有input,output delay都指定到那个虚拟时钟上,CTS后,只要在虚拟时钟上加上(BC 0.1 WC 0.2)的latency就好了

记得的后端面试题目就这么多了,

现在已经开始在新的公司打工,以后遇到问题,再同大家分享

结束了?

谢谢陈大无私分享,也祝今后工作顺利哈!

WC下 setup/hold WNS -0.2

BC下 setup/hold WNS -0.1

哈哈,我在第二问有些不大理解,我那个方法你可以试试,在block level很好用的.

我不理解的地方是:在place之后,in和out那俩timingpath,能同时满足setup和hold 为0ns么?当in 的setup为0的时候,hold是不是很明显的差了一个cycle?如果那个假设能成立的话,我能想到的就只有一个办法:把input delay 和output delay的min 都设为0, 不知道还有什么样的情况能实现?多多指教哈.

那是为了简化问题,假设的一个理想条件

这个我没记错的话是set_input_delay 和set_output_delay的问题。里面有个选项就是-clock 和 -include_latency(我没记错的话),意思是定义这个port相关的时钟时是否包含它的latency。这个题目考的就这个概念吧。

感谢小编的分享,学到好多知识!

可以详细说说为啥是reg2out是setup violation? 而in2reg是hold violation?

还有setup violation=0.2;setup violation=0.1是怎么得来的吗?

谢谢!

那个大哥帮说说!

lz1920,你好,请教你的这个解决办法,

1 为什么在real clock constraint io的时候,update_clock_latency之后,就不设置set_propagated_clock, 如果设置了会怎么样?

2 同样的情况,用virtual clock constraint io的时候,update_clock_latency只有,也不需要设置propagated_clock吗?

谢谢先。

看不懂啊……

可能是我bc_wc和mcmm的概念有点混乱,我想请问一下,在bc_wc模式下,wc corner就不考虑hold的check吗?

可以这样理解,insertion delay是由于插在clock path上的delay导致的latency,目的是cts为了min skew,那么,在clk port插入的delay使得clock path相对于data path整体延时了insertion delay,这样的话,由于datapath不变,相对来说,in2reg clockpath被“拉伸”了,相对而言,hold vio, reg2out clockpath被“压缩”了,setup vio. reg2reg没变化。在外部约束条件没有变化的情况下,原来place之后做平的setup, hold在经过cts后,做sta会有vios。所以,前面的老师会提出解决办法:input_delay+delay,output_delay-insertion delay。

input_delay

output_delay

计算hold vio是bc,所以是-0.1ns,setup vio是wc,所以是-0.2ns。

修改virtusl clock的uncertainty -setup/hold

您好,问下,如何在PT中实现你说的这样的功能?谢谢!

是不是都是-0.2啊

是不是都是-0.2求指点