后端面试--每日一题(017)

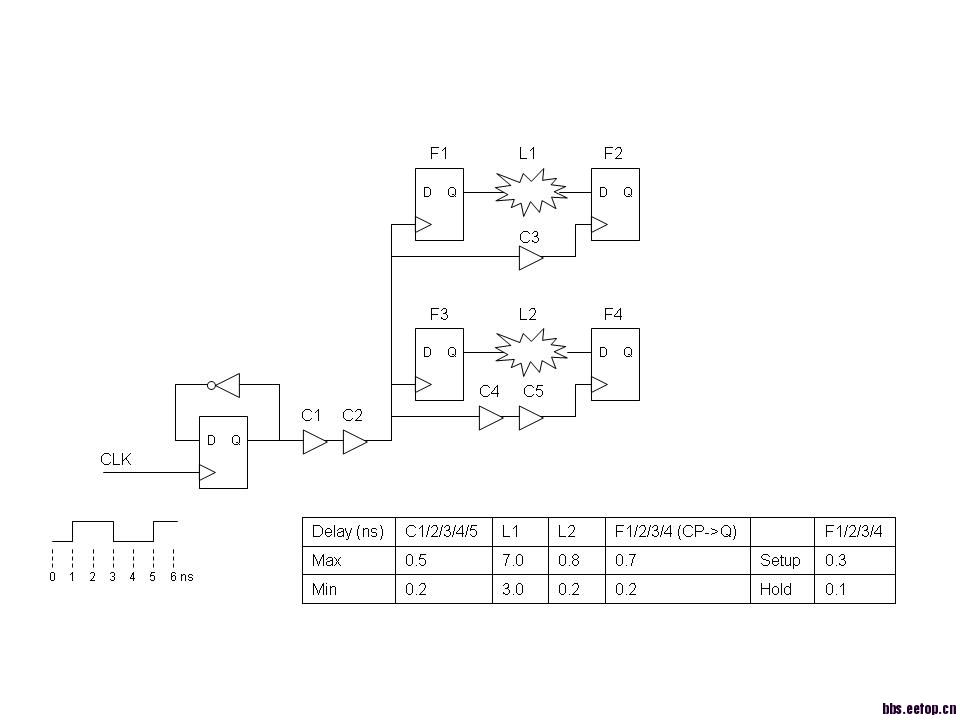

giving the schematic and delay in attached picture, calculate theWC setup slack at D pin of F2, and BC hold slack at D pin ofF4

如图所示电路,时钟和延迟,计算WC下到F2输入端D的setup slack,BC下到F4输入端D的hold slack

难度:3

我算出的是:F2输入端D的setup slack是(8+0.5-0.3)-(0.7+7.0)=0.5

F4输入端D的hold slack是(0.2+0.2)-(0.2+0.2+0.1)=-0.1

setup都使用max值,hold都使用min的值

采用OCV模式的话,F2输入端D的setup slack是(8+0.2-0.3)-(0.7+7.0)=0.2

F4输入端D的hold slack是(0.2+0.2)-(0.5+0.5+0.1)=-0.7

我没有把握,只是想来验证一下自己的答案,因为对前面那个generator clock全当做clock latency处理了,data path和clock path的clock latency都一样,所以计算的时候都可以不考虑,只是时钟周期换成8了,

等待正确答案啊,呵呵

OCV一般不这样设置,算10%的variation 的话, setup 也就是 8+ 0.5 -0.05 -0.3 -7.7 = 0.45 吧。

hold time 也成了 -0.14 吧

嗯。 setup: 0.5 ,hold -0.1

二楼的,已经指明是bc,wc,你这个是过度回答,^_^

因为没有给OCV的derating,所以计算时不用考虑OCV

呵呵 弱弱地问下derating是什么呀

嗯 同意2楼非OCV解答

这个就是正确答案

大大, 恕晚辈冒昧,setup slack有异议,图中给出的clk的period是4ns, 非8ns, setup slack貌似不met!

大大, 恕晚辈冒昧,setup slack有异议,图中给出的clk的period是4ns, 非8ns, setup slack貌似不met!

楼上的同学你掉坑里了

何处此言,望大大解惑!

门控是用dff实现的,不是用latch,所以是8,请陈小编确认

有个分频器在那

有分频,看不到吗?

Hold Time有一个疑问?

Hold Time顾明思意就是要数据保持时间(F3的)要比时钟来得长(F1的),为什么不是如下计算方式?

[DF3(cp->Q min) + DL2(min) ]- [ DC4(max) + DC5(max) +F4 (setupmax)]

即(0.2+0.2)-(0.5+0.5+0.3) = -1.1

嘿嘿,又做对了一道

这样的算法太悲观了,实际中没有可能发生的吧。 一般bcwc 计算都用bc算hold。 bc情况下,cell,net的delay都比较小。

要用ocv的算法,应该是厂家有提供专门的ocv的lib来算吧。要不然实在太悲观了

问下为啥是8ns,而不是4ns呢?

时钟分频了

这给OCV的求解中,clock path有variation,data path是不是也要做variation啊L1中要加0.07.

求正解?

求问小编,为什么计算setup时间的时候,C3的延迟按max0.5来算,我觉得这应该按min0.2来算才对呀

求问为什么计算setup时间的时候,C3的延迟按max0.5来算,我觉得这应该按min0.2来算才对呀

launch按WC算,capture clock按BC算,太悲观,不现实

小编啊,launch这里也没有考虑BC呀,这里没有考虑两个时钟的共同路径呀,这里的计算方法应该不存在CRPR的问题。两个只差一个C3,也就是两个时钟的skew也就是一个C3的延迟。所以只是把C3的延迟设为最大,应该只能这样做吧?

小编啊,launch这里也没有考虑BC呀,这里没有考虑两个时钟的共同路径呀,这里的计算方法应该不存在CRPR的问题。两个只差一个C3,也就是两个时钟的skew也就是一个C3的延迟。所以只是把C3的延迟设为最大,应该只能这样做吧?

因为“也就是两个时钟的skew也就是一个C3的延迟。所以只是把C3的延迟设为最大” ,所以“按max0.5来算”

小编,今年兆易的笔试题全都是你的后端面试总结里面,是不是考虑收下版权费啊~

真有这事?!

那他们怎么测得出应试者的水平,答案早就公开了。

那个什么,看过答案后,考得比较好的,主动把钱送来!

前面利用DFF实现2分频所以时钟周期从4ns变成了8ns