后端面试--每日一题(031)

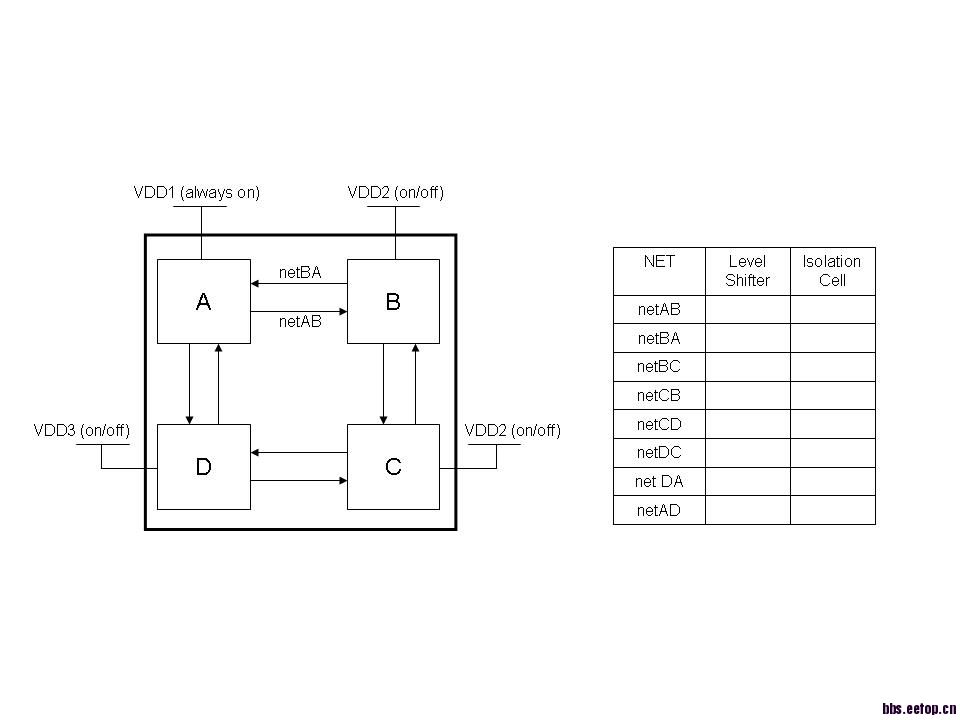

There are 4 power supplies in the design. VDD1/2/3 are different voltage. VDD1 is always on, but VDD2 and VDD3 can be turn off and on. VDD2 to block B and block C don't switch at same time. Please fill in the blank which net needs to be added level shifter and/or isolation cell. If you think Level shifter/isolation cell should be added in netAB at B side, then write B; if you think it's not necessary, write X.

如图,一个设计中有4个电源,VDD1/2/3的电压各不相同,VDD1总是开着,其他会有开和关,并且到模块B的VDD2和到模块C的VDD2有各自分别的开关。请判断在连接这4个模块的8条net上,哪些需要level shifter,哪些需要ioslation cell,把结果填入右边的表中。

填法如下:假如你认为需要在netAB上加个level shifter,加的位置在模块B里面,就在netAB的右边的第一列空格里写B。如果什么都不加,就写X

难度:3

没做过low power设计,但是研读过low power methodology manual for soc这本书。我来说说我的理解,有不对之处请高手指教。

一、电平不同的模块之间即需要level shifter,故netAB/BA/AD/DA/CD/DC都需要level shifter。至于level shifter的位置是放在src端还是des端。一般来说H2L的由于只包含有des的power rail,所以肯定要放在des端。而L2H则包含有两种power rail。肯定需要跨电压域的电源线连接。考虑到output driver需要的电流一般要大于input driver需要的电流。所以也推荐放在des端。在本题中也未提到电平之间的相对大小。所以我都放在des端。

二、有power gated控制的模块,其输出都要加上isolation cell,故netBA/BC/CB/CD/DC/DA都需要isolation cell。其位置的摆放也有两种,一是摆放在ouput端,一是摆放在input端。前者一是可以节省所需要的isolation cell数量(考虑一个模块引脚的输出连到多个模块引脚的输入的情况),二是便于check。后者优点是isolation cell需要always-on的power。若放在output端,还需要引always-on的power rail过来。故此例中BA和DA的isolation cell都放在了A模块中,其它的则放在ouput端。

我的答案是:

netAB B X;netBA A A;netBC X B;netCB X C;net CD D C;net DC C D;net DA A A;net AD D X;

应该是“后者优点是isolation cell不需要always-on的power”吧?

isolation cell理论上可以放在output端,但是考虑power-on rail的走线,isolation cell自身的功耗,一般还是放在input端比较好。

你的答案也是正确的!

我明白了。放在input端的话,不需要额外的power-on rail的走线,用本模块的power就可以了。特别对于本题来说,不存在一个output连在多个input上面的情况。放在output端也不会比放在input端更节省所需isolation cell的数量。谢谢!

学习了

iso 放在input端不好吧,

比如一个本来不power gating 的模块A,接收了来自power gating 模块B的信号,

iso 却插在模块A,这样明显会增加验证的难度,

iso 都插在模块的边界,引入always on的power ring 有什么难度吗?

一个简单的iso逻辑,为什么插在A中就“明显会增加验证的难度”,而B中就不会?如果是同样难度的话,就要考虑对power plan的影响了

本来是可以避免在B中引入always on的power ring,因为iso位置的原因,平白增加了这个任务,难度先不计,最后你还要用power LEC去验证那个always on的ring,你觉得哪个更省事?

高深!学习一下。

学习了

学习了 高深 赞一个

实际中很难遇到这种情况的, 个人感觉还是实际的项目实际点,

学习了,我们的isolation是插在always on的模块里的

学习了

学习了,我的isolation也是插在always on的模块里的