新手,请教下下面这个图里的时钟该怎样定义

时间:10-02

整理:3721RD

点击:

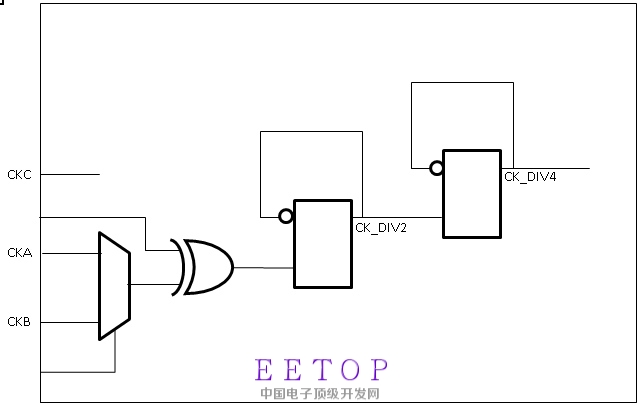

图中CKA、CKB、CKC互为异步时钟。选择器的S端和异或门的另一个输入都可以认为是固定不变的。

在综合时,应该怎样约束时钟,我有几个问题想请教大神

1、在设置clock group时,CKA、CKB、CKC该怎样划分?

2、CK_div2显然要设generated clock,那它的source应该设置为CKA/CKB,还是选择器的输出,还是异或门的输出?如果是设CKA/CKB的话,是不是要设2个generated clock?

3、CK_div4应该针对CK_div2设2分频的generated clock,还是应该针对CKA/CKB设4分频的generated clock?

不要沉了呀。自己顶一下。继续求大神指导。

1、在设置clock group时,CKA、CKB、CKC该怎样划分?

互为异步,三个group,

2、CK_div2显然要设generated clock,那它的source应该设置为CKA/CKB,还是选择器的输出,还是异或门的输出?如果是设CKA/CKB的话,是不是要设2个generated clock?

source应该设置为CKA/CKB,可以只设一个gen,选clock rate高的那个约束;

3、CK_div4应该针对CK_div2设2分频的generated clock,还是应该针对CKA/CKB设4分频的generated clock?

CKA/CKB设4分频的generated clock。

个人意见:

1.先用create_clock创建CKA、CKB、CKC,然后将CKA、CKB定义为set_clock_groups -logically_exclusive,又因为这三个时钟互为异步,所以再定义set_false_path -from CKC -to CKA/CKB set_false_path -from CKA/CKB -to CKC

2.source 写在MUX的输出吧,

3.写两个generated clock,他们是source就写他们的对应的reg的CK端即可,都是二分频,在这里还要指定他们的master_clock,因为你的MUX、XOR的另一端是确定的,所以master_clock也应该容易确定