IC Compiler 不在Macro上层绕线

Macro的LEF里面定义了OVERLAP layer,而且是占Macro整块面积。我试过修改这个layer使其面积变小,但结果只会让ICC在这个Macro下面放了很多Standard Cells,第5层金属依然没有线。

谢谢帮助!

你需要看看这个MACRO是不是有那层的route blk,如果有,你应该没有改对地方

谢谢回复!我看过Macro的LEF,里面没有METAL5 Blockage,所以很不理解。我正在研究怎么用ICC检查Blockage。

目测,你那些不是straps吧,感觉像是连接stdcell的special pg线。

确认你没弄错吧?你说的情况,M5从macro上跨过,没有任何问题,可以实现。

你试过手动在那上面拉metal5没?能走线不?

这些线是用ICC的template-based power network做的。我在做一些试验,这些straps位于METAL5,画的比较细,而且和底层stand cell的PG rail对齐,通过via连到下面的金属。template脚本附上了。我没有做power net的经验,请大牛再指点。

- template : mesh_m5_b {

- layer : METAL5 {

- direction : horizontal

- width : 2.4

- spacing : minimum

- number :

- pitch : 12.8

- offset_start : boundary

- offset_type : edge

- offset :

- trim_strap : true

- }

- advanced_rule : on {

- optimize_routing_tracks : off {

- }

- align_strap_with_stdcell_rail : on {

- layer : METAL5

- align_with_rail : true

- put_strap_in_row : false

- }

- }

- }

我现在基本都是用脚本做的布线,还不太熟悉怎么去手修。我试验过先不摆放Macros,在METAL5上先画满PG线,然后再摆放Macros和Std Cells。这样倒是实现了我想要的走线和布局(附图),但是Std Cells出现了少量placement errors。

常规应该都是先摆放Macros再做PG Net吧?我感觉可能是脚本里有地方设置不对导致先放Macros然后做PG的时候出现问题。

0.25的设计,金属过电流能力应该很大吧,你的stripe做的这么密是不是有点过了?相应的绕线资源是不是也受影响?

怎么做都可以,没有绝对的对错,只有针对你的设计的合理的方案罢了。

通常 Top Metal Space Rule 比其他 Metal 寬, 可能你畫的Metal5 PG strap pair gap 不夠它 Route.

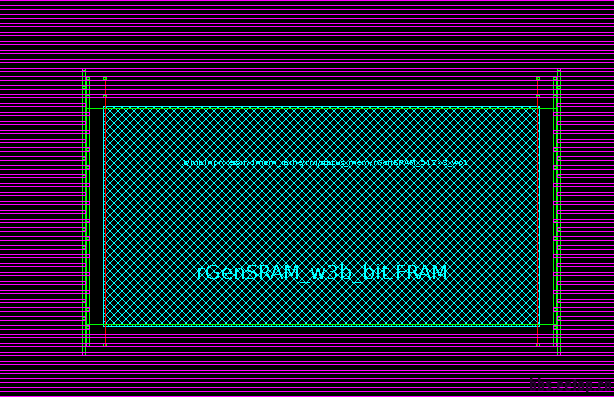

谢谢各位帮助!问题基本解决了,我的Macro库是用Milkyway的LEF IN做的。虽然LEF里没有用到Metal5以上的金属,但是Milkyway在做BPV的时候默认在Macro区域的每层金属都做了Blockage。脚本里有一个地方

setFormField make_macro metal_5 "block all",这里改成"merge",在Metal5就没有blockage了,straps也都通过了Macros上面。

第一次做后端,明显power部分做过分了。后期会根据布线实际情况再做调整。

谢谢!我用的这个compile_power_plan方法如果遇到了你说的这种情况,会报Error。我开始确实遇到了这样的情况,根据ICC的提示对间距做了调整。

我导的macro也是block all,做P/G strap会通过macro上方,请问有啥解决方法啊?

你的意思是不想让PG经过Macro上方?

是的,每一次我都得自己做blockage

这好像和我遇到的情况正好相反,请问你用的什么工具和命令做的power strap?我用的是IC Compiler的compile_power_plan。

ICC /create_power_straps ....

我简单试了一下这个命令,如果导入LEF的时候用"block all",这个命令也不会过我的Macro上面的。你再检查一下Milkyway的流程吧。

好的,我看了下route blockage没出来,我用的BPV

我们一般用abstract提取lef,abstract 可以对blockage 做具体设置

多多學習,這可能跟準備FRAM VIEW有關