标准单元库 LVS验证 出现property error

时间:10-02

整理:3721RD

点击:

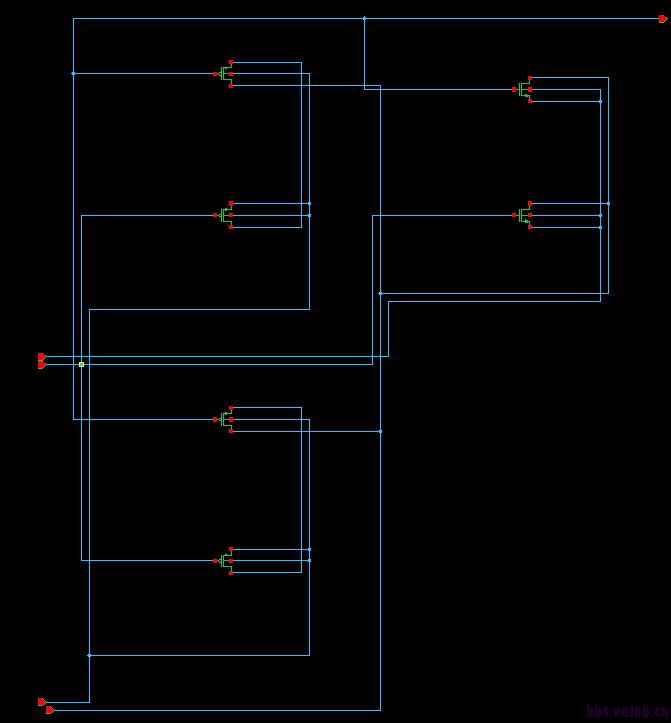

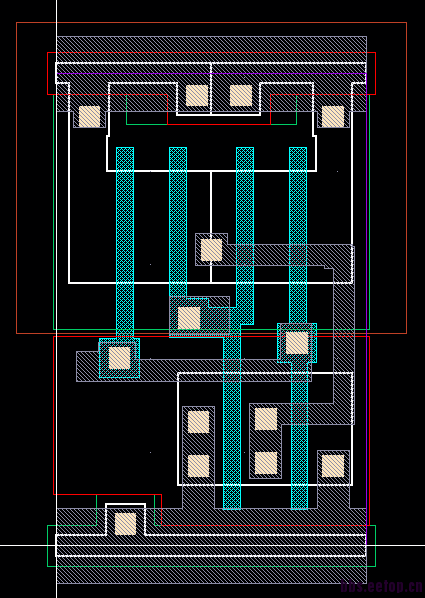

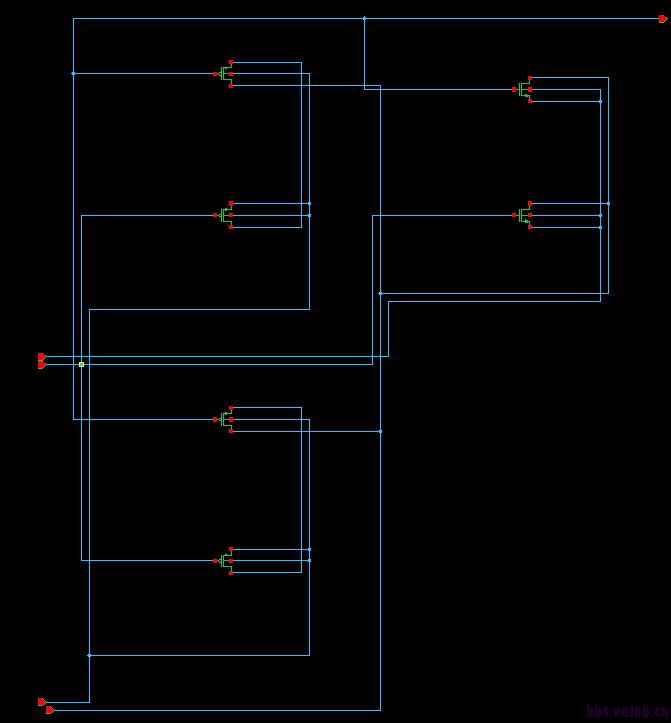

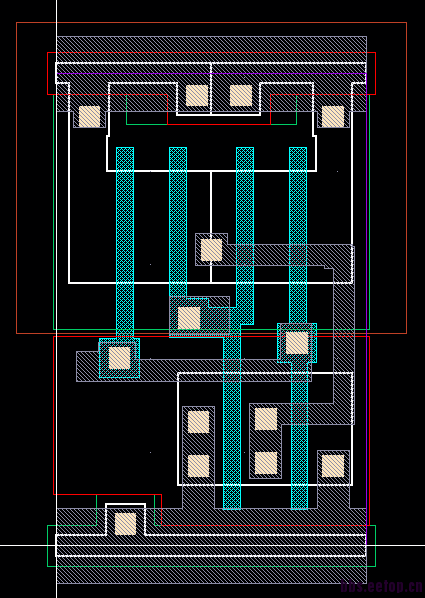

大家好,我最近在做版图设计时(chart 0.18 um工艺)用了arm的标准单元库里的一些cell,但其中的NOR和NAND在做LVS时总会有property error,而AND、INV、BUF和DFFR都正常(只用到了这些)。单独做NOR的LVS也有property error,report 如下:

CELL COMPARISON RESULTS ( TOP LEVEL )

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Property errors.

LAYOUT CELL NAME:NOR2X2

SOURCE CELL NAME:NOR2X2

--------------------------------------------------------------------------------------------------------------

INITIAL NUMBERS OF OBJECTS

--------------------------

LayoutSourceComponent Type

--------------------------

Ports:55

Nets:77

Instances:22MN (4 pins)

44MP (4 pins)

10*D (2 pins)

------------

Total Inst:76

NUMBERS OF OBJECTS AFTER TRANSFORMATION

---------------------------------------

LayoutSourceComponent Type

--------------------------

Ports:55

Nets:55

Instances:11_nor2v (5 pins)

------------

Total Inst:11

* = Number of objects in layout different from number in source.

**************************************************************************************************

PROPERTY ERRORS

DISC#LAYOUTSOURCEERROR

**************************************************************************************************

1M4(1.920,2.800)MP(PMOS_1P8)Mm5MP(PMOS_1P8)

m: -3.40282e+38m: -3.40282e+38

2M5(2.480,2.800)MP(PMOS_1P8)Mm3MP(PMOS_1P8)

m: -3.40282e+38m: -3.40282e+38

**************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************

MatchedMatchedUnmatchedUnmatchedComponent

LayoutSourceLayoutSourceType

-----------------------------------------

Ports:5500

Nets:5500

Instances:1100_nor2v

--------------------------------

Total Inst:1100

o Statistics:

1 layout instance was filtered and its pins removed from adjoining nets.

4 layout mos transistors were reduced to 2.1 connecting net was deleted.

2 mos transistors and 1 connecting net were deleted by split-gate reduction.

4 source mos transistors were reduced to 2.1 connecting net was deleted.

2 mos transistors and 1 connecting net were deleted by split-gate reduction.

o Initial Correspondence Points:

Ports:VDD VSS Y A B

其中的红色加粗部分就是出现的错误信息,不知道这是什么错误,m: -3.40282e+38又是什么参数,还望大神指点,多谢!

CELL COMPARISON RESULTS ( TOP LEVEL )

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Property errors.

LAYOUT CELL NAME:NOR2X2

SOURCE CELL NAME:NOR2X2

--------------------------------------------------------------------------------------------------------------

INITIAL NUMBERS OF OBJECTS

--------------------------

LayoutSourceComponent Type

--------------------------

Ports:55

Nets:77

Instances:22MN (4 pins)

44MP (4 pins)

10*D (2 pins)

------------

Total Inst:76

NUMBERS OF OBJECTS AFTER TRANSFORMATION

---------------------------------------

LayoutSourceComponent Type

--------------------------

Ports:55

Nets:55

Instances:11_nor2v (5 pins)

------------

Total Inst:11

* = Number of objects in layout different from number in source.

**************************************************************************************************

PROPERTY ERRORS

DISC#LAYOUTSOURCEERROR

**************************************************************************************************

1M4(1.920,2.800)MP(PMOS_1P8)Mm5MP(PMOS_1P8)

m: -3.40282e+38m: -3.40282e+38

2M5(2.480,2.800)MP(PMOS_1P8)Mm3MP(PMOS_1P8)

m: -3.40282e+38m: -3.40282e+38

**************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************

MatchedMatchedUnmatchedUnmatchedComponent

LayoutSourceLayoutSourceType

-----------------------------------------

Ports:5500

Nets:5500

Instances:1100_nor2v

--------------------------------

Total Inst:1100

o Statistics:

1 layout instance was filtered and its pins removed from adjoining nets.

4 layout mos transistors were reduced to 2.1 connecting net was deleted.

2 mos transistors and 1 connecting net were deleted by split-gate reduction.

4 source mos transistors were reduced to 2.1 connecting net was deleted.

2 mos transistors and 1 connecting net were deleted by split-gate reduction.

o Initial Correspondence Points:

Ports:VDD VSS Y A B

其中的红色加粗部分就是出现的错误信息,不知道这是什么错误,m: -3.40282e+38又是什么参数,还望大神指点,多谢!

看你的trace property 容差是多少, 1~5% 都是可以忍受的,

或者问下vendor也行

你好,我试着将tolerance改成了5%,但还是有那个错误。请问通常报property error,除了原理图和版图中管子尺寸不匹配,还有可能是什么原因啊?

因为看这错误应该不是尺寸不匹配。

多谢

DISC#LAYOUTSOURCEERROR

****************************************************************************************

1M4(1.920,2.800)MP(PMOS_1P8)Mm5MP(PMOS_1P8)

m: -3.40282e+38m: -3.40282e+38

2M5(2.480,2.800)MP(PMOS_1P8)Mm3MP(PMOS_1P8)

m: -3.40282e+38m: -3.40282e+38

结果看不懂, 太老的库了,问vendor吧,

兄弟问题解决了么?咋解决的?

我也遇到类似的了