set_wire_mode和set_wire_model

时间:10-02

整理:3721RD

点击:

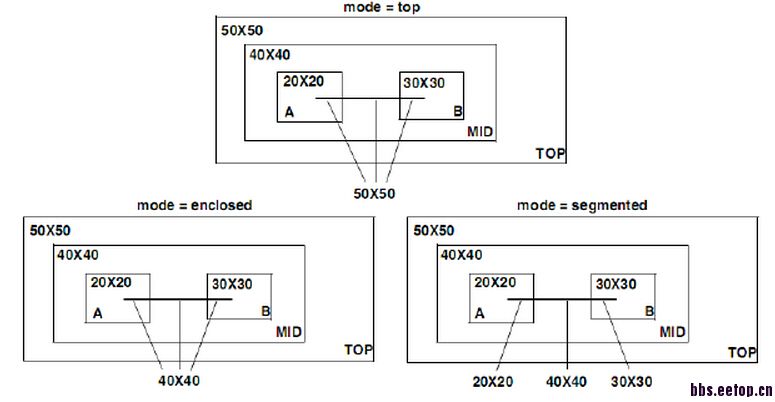

mode的三种情况,segment,top和enclosed,

模块中的wire_model分别是 20*2030*30 中间模块的是 40*40 顶层模块的是 50*50

求大神们能解释下这个图

50*50。应该是block的大小吧,对应到lib里面去,top,segment,enclose是对内嵌的这些block的net使用不同model的一种分配方法吧,我理解的比较浅显

在做线延时预估的时候需要根据chip的大小或者block去预测线延时的length,一般block越大,length越大,延时就越大,所以根据block的大小,lib里设定了不同的预估方法,就model,但是对上面的三幅图,又有不同的三种mode,top就是根据顶层block的小去确定model,enclose是将图中的那条net(特例)根据上一层去确定model,最后一个就是按block的区域去确定不同的model

应该有不对的地方,求指正

恩,你说的可能也是底下这个意思,下面这个是标准答案,你看看,应该和你说的一个意思

set_wire_load_mode

如果只是在子模块综合中设置了线负载模型,那么跨模块边界的连线延迟如何估计,该命令就是用于设置模块互连线延迟估计所使用的模块

该模式有三种选择:

Top指定模块互连线延迟的估计使用顶层模块的线负载模型

Enclosed指定模块互连线延迟的估计使用包含该连线的最小模块的线负载模型

Segmented将连线按模型边界分段,各段的延迟分别按照各自模块的线负载模型估计延迟,然后把估计结果相加得到该连线的延迟

嗯,这个解释好,学习下

明白了~

一张图,清晰明了,纠结了这么久的事情,终于门清啦,撒花