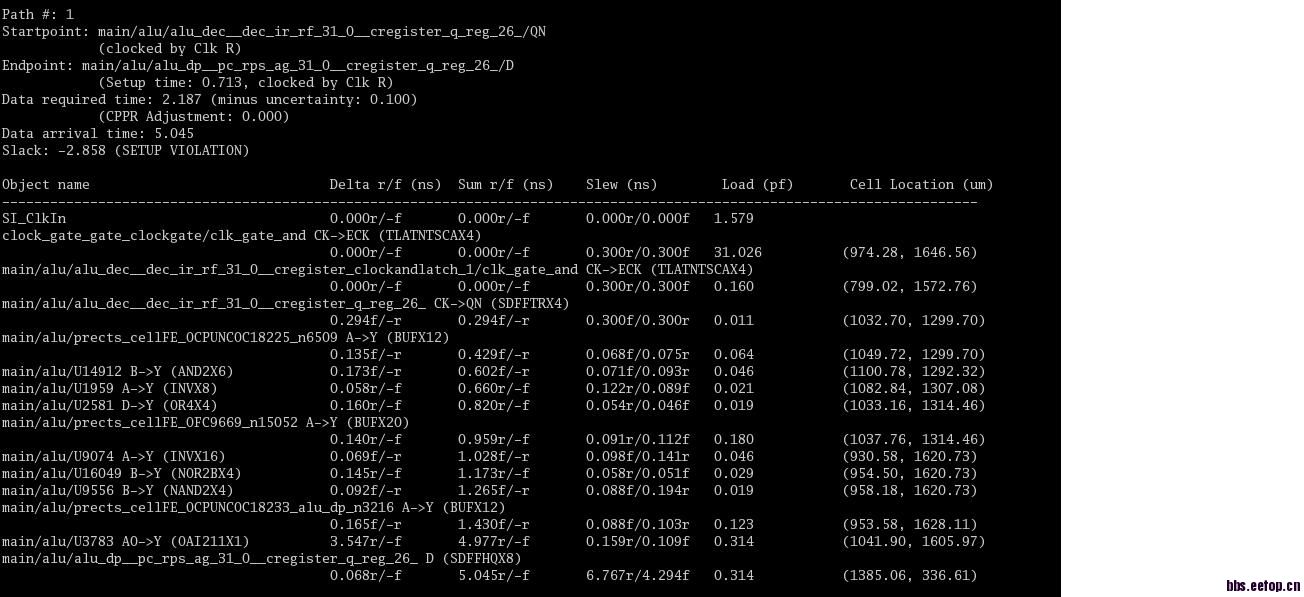

这样的setup violation如何解决

工具修了很多次都是这样的,该怎么办呢?如果手动修怎么办呢?

U3783的延迟太大了,先找原因,再想办法

U3783是系统的一个逻辑单元,把他变成X4的?

我知道那是逻辑单元,你要做的是,先找出来为什么那个单元上的延迟那么大! 置顶的FAQ里面列举了一些常见的情况

在不明原因的时候,谁知道sizeup管不管用

我看了FAQ的内容,我认为可能是ff之间距离太远了,是用group_path来拉近他们的距离吗?

grouppath

or

insert buffer into long net

insert buffer into long net是不是说加了buffer,长线的延时就变短了?

小编, 您好有耐心啊,您越来越尊敬您了,真的。

在prectsopt时,data path 的arrived time和required time的slack为-0.6,观察也没发现问题,这样的话,能不能在CLK上加Buffer啊?如果能的话为了防止在CTS时被优化,把他设置成fixed,不知道这样做行不行啊?

修改clk skew当然是一个方法

如果是我做的话,一定先搞清楚为什么slack为-0.6

在报告当中有一个NOR2X8,它的slew值明显比别的大,别的器件都是0.1左右,他的是1.6,问题可能出在这,要想解决它,应该怎么办呢?

你要找到为什么它的slew大?

每日一题里面有一道从STA找setup violation原因的题,先去学学,用同样的方法在你的设计中找一下

研究过了,终于有点意思了,谢谢陈小编

icc中怎么样报出这么详细的报告啊?

陈大大,我看它那个delay很大的cell是x1的,分析是驱动太小了,所以delay大,而他说是因为两个reg离得太远了?离得太远为啥就造成这个cell的delay很大?