edi 时钟树为何这样做?

时间:10-02

整理:3721RD

点击:

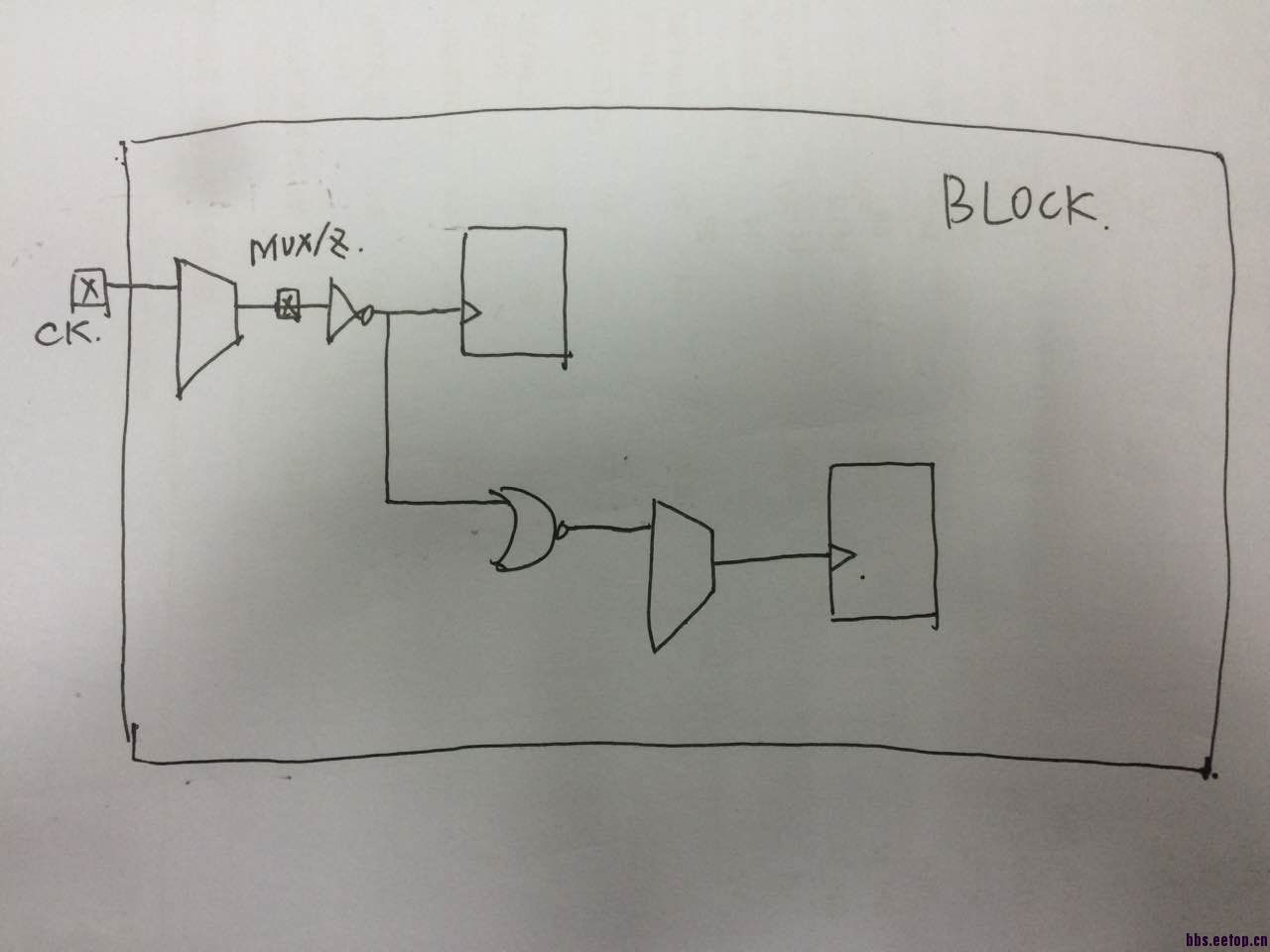

在edi中,将clock root设置在block的端口CK,时钟树做完后,会在CK端口和它之后第一个MUX之间插入两级buf,这是什么原因,我怎样让工具不插入这两个buff?谢谢!

给的信息量太少了,没办法具体回答这个问题,不过我想你可以试试从下面找原因:

1. 是不是这个mux的transition太大,不能meet DRV,所以前面要插buffer?

2. 是不是为了平衡clock skew加入了buffer?这个要分析整个clock tree的影响。

如果在不违反DRV的情况下,可以考虑用ECO删除这两个buffer。

谢谢您的建议,我再查查看!另外时钟树就是这个简单的结构,就这么几个门。